Editor's Note: This Japanese translation of ESNUG 530 #2 has been

provided by Shinji Iyobe of DSM Solutions in Shibuya, JP. - John

( ESNUG 531 Item 5 ) -------------------------------------------- [08/08/13]

Subject: (Japanese) User on Defacto's RTL & gate editing, coding, ECO tool

> NEW! -- DeFacTo Signoff ATPG has some truely curious test stuff where it

> can do ATPG on your Verilog RTL *before* you do any synthesis. I'm not

> exactly sure how it works. (booth 409) Ask for Chouki Aktouf.

>

> - from http://www.deepchip.com/gadfly/gad053013.html

From: [ Asterix the Gaul ]

こんにちは、ジョン、

私と私の会社については匿名としてください。

私は今年のDAC Cheesy Must See リストの中で、あなたがDefactoについて興味を持ってい

る事を知りました。

私たちは3ヶ月間の評価後、約3年前にDefacto STAR RTL Platformを購入し、それ以来使用

してます。

STAR RTLは、RTLの作成、IPの接続、トレース、操作、RTLの変更を行う設計者を支援する為の多

くの違うユーティリティを持った"設計者のツールボックス"のようです。--それらは検証に

も役立ちます。

STARの導入以前、私たちの設計者はテキスト・エディタ(emac/vi)と内部のスクリプトを使用し、

すべて手作業で行っていました。

STAR"ツールボックス"はAPIを持ちます。私たち自身のユーティリティを作成するためにTclまたは

Perlを使用することができます。さらにDefactoのTclと非Tclの追加をいくつか持っています。

---- ---- ---- ---- ---- ---- ----

STARのコアとなる機能:RTL及びゲート・レベルのエディティングとコード生成

1. SoC/IPのインテグレーションと新しいVerilog/VHDLコードの生成

STARは自動的に必要とする接続を行い、異なるIPをインスタンス化するためにRTLの生成します。

その入力は以下の通りです:

- RTL又はゲート・レベル・ネットリスト

- ライブラリ

- 接続をしたい周辺のIPのための数行のコード

私たちのIPが変更されるたびに、STARは自動的にそれらを接続するために正しいフックを作成

します--IPの多くは、その周りと常に存在するスタンダードのポートのセットの周りにラッパ

ーを持ちます。IPが変更された時に、これは統合に役立ちます--私たちの設計者の為に、よ

りわかり易さを維持します。

私たちの設計において100のIPをしばしば統合します。手書きによるそれぞれのRTLのラッパー

の作成とそれらの検証に数日要します。私たちの問題は時間だけでなく、関連する依存関係も

あります--手作業のエラーによるプロジェクトの遅延の影響です。STARはラッパーのコード

を自動的に作成するだけでなく、何か行なおうとする修正が正しくない場合にも直ちにフラ

ッグを立てます;例えば、出力から出力に接続する場合や異なるバスの長さを接続する場

合などです。

RTL言語のサポートについて、私たちはVerilog, System Verilog及びVHDLを使用します。

Defactoはそれらすべての言語をサポートしてますが、これまでに問題はありません。Defacto

は混在の言語サポートを主張していますが、私たちはそれを必要としたり、試みたことはあ

りません。

接続を生成するためにSTARを使用するIPの種類:

- デザインIP:3rdパーティと内製の両方

- メモリー:STARは自動的にいろいろなメモリーのサイズ、

形状及びパワーを取り扱います

- DFTロジック:STARはDFT用IPの自動的なインスタンス化と

接続に役立ちます--JTAGタップ・コントローラー など

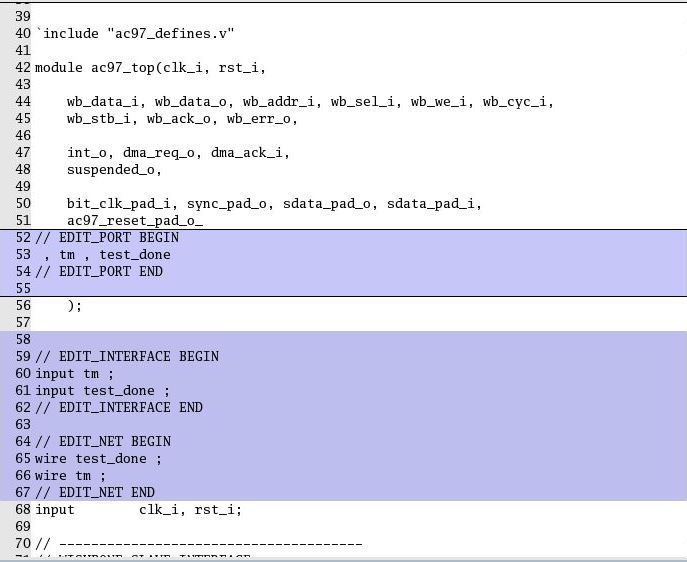

図1.自動的に生成されたDefacto STARの接続ラッパーのコード

(CLICK ON PIC TO ENLARGE IMAGE.)

Defactoは、RTLが正しくて合成可能である事を保証するために独自の基本的なチェック機能を持

っています。一度それが完了すると、私たちは新しいRTLネットリストをCADENCE NC-Verilog

かVCSか ModelSimでシミュレーションを行います。また、DFTロジックの追加によってチップ

の機能が変化していない事を保証する為にDFTに関連した接続を生成する為にSTARを使用す

る場合、フォーマル検証(Conformal LECもしくはFormality)を実行します。

私たちは独自の追加ルールを作成するためにDefacto APIの使用ができます、もしくは、Defacto

の追加のストラクチャー検証のアプリケーションを使用できます。それについては後

で意見を述べます。

2. Design Exploration(設計の探求)

"Design exploration"はSTARの不可欠な基本部です--私たちはSynopsys DCがゲート・レ

ベルで探求するのと同様の方法でRTLを探求するのに使用します。

- 私たちはポートとインスタンスを見つけるために基本的なクエリ・コマ

ンドの実行することができます;そのサーチは本当に早いです--通常1秒

くらいです

- STARはまた、ファンイン、ファンアウトやパスのような先進的なフル・デ

ザインの階層のクエリをサポートしてます。

私たちはこの機能を随時使用します--われわれのRTL、アクセス、クエリなどを探求することがで

きることは非常に便利です。

3. ユーザー定義のデザイン・ルール・チェック(DRC)

私たちはRTLとゲート・レベルのパワーのチェックのためにSynopsys MVRCとCadence CLPのロ

ー・パワー設計ツールを使用してます。しかし、いつも早すぎて、EDAベンダーがまだサポートして

いないチェックを行います。

1.興味を持つ設計要素のトレースと定義をするためにSTARを使用します。

2.設計要素に適用するカスタム・デザイン・ルール・チェックを記述する

ためにTclとPerlを書きます。

例:

- ロー・パワー・ルール。ロー・パワー検証の為に、私たちはパワー・

スイッチ接続のためのDRCを実行します。これまでのところ、いつも

問題を見つけました。

- DFTルール。DFTの為の独自ルールを書くためにSTARを使用しますが、

高度なDFTルール・チェックには、DEFACTOのSign-off DFTルール・

チェッカーを使用します。

- メモリー接続チェック--すべてのメモリーが正しく接続されている事

を保証するために--特にロー・パワーとDFTに関係したすべてのポート

について。

4. Pin-to-Pinのトレース

私たちはクロック上の構造接続のチェックと長いシミュレーションをすることなしにI/Oマルチプ

レクサ・ロジックのために広範囲にSTARを使用します。主な目的は、制約のセットを適用した後、

2つのノードが構造的に接続されている事を保証する為です。

例:

- 特定のブロックの出力が特定のピンのマルチプレクサ・モードで

特定のチップI/Oに直接接続されている事。

- DFTのように特定のクロックが定義されたモードでPLLから特定の

ブロックの入力に伝播している事。

これらのpin-to-pinのトレース・チェック(制約下の)はたくさんの時間と労力を節約しま

す--特に妨害の位置を正確に示すことができるGUIで(もし、何かあれば)。私たちは、

その次のRTLが接続の意図を満たすことを保証するためのリグレッションとしてDefactoのチ

ェックを使用します。

---- ---- ---- ---- ---- ---- ----

STARの追加アプリ

Defacto STARプラットフォームは人々がiPhonesに機能を加えるのと同様の方法でユーザーによ

る拡張が可能です。モジュールもしくはアプリを追加します。私たちが現在使用しているいくつ

かはここにあります。

1. STAR-ECO—フルECOツール

STARは自動化されたECO機能を持ちます、IP自体のECOよりも、接続の追加と削除ような接続

の変更を主に行います。

STARのECOはRTLとゲート・レベルで動作しますが、私たちは主にゲート・レベルのECOのため

に使用 します。ゲートのセット追加をしたい場合、インバータのように、特定の方法で、私た

ちは特定タイプのネットのサーチやインバータの追加のためにSTARを使用します。手作業で

それを行う場合と比べてECOを行うために1つ(または少数の)のコマンド・ラインだけ

を必要とするだけです—新しいネットリスト加えるために手作業で階層を横断すること。

私たちはまたゲート・レベルでより複雑なECOを自動的に行うためにSTARを使用します:

- バッファをインバータに変更

- バッファのセットをインバータのセットに変更

- ANDゲートをNORゲートに変更

- フライでスキャン・チェーンをスティチィング;フロップの定義、

スキャン・チェーンの挿入、クロックの接続.

私たちのファンクショナルECOの多くは合成とLECを通します。合成の実行もしくは論理の等

価性のフォーマル・チェックの実行の必要性なしに自動的にゲート・レベルの変更行うために、

ときどき私たちはSTARを使用します。

例えば、私たちがロー・パワーの調整を行うとき:パワー・スイッチの接続、ISOセル

の接続、いろいろなアナログIP および/またはメモリーへのレベル・シフターの接続

とロー・パワー接続--フォーマル・ツールはれ自体、機能に影響をあたえないので変更

を見ることができません。Synopsysの Design Compilerはパワー・スイッチを知ること

も見ることもしません。DFTのECOについても同様です。変更はデバイスの機能には影響

しませんが、テスタビリティに影響を与えます。私たちはECOを実装するためにフォー

マルの方法は使用できません;その代わりにSTARを使用します。

私たちのSTARへの唯一の代替策は手作業でECOを行う事です。5階層の深さのノード

である場合、手作業による全てのポートの接続は苦痛です。

- 手作業によるECO:モジュールA、モジュールCなどを修正してからインター

フェースを変更し、ポートの追加しなければなりません。

- STARによるECO:1行だけ必要です。

STARは早いです。平均時間の節約のアイデアをあなたに与えるために、私たちの

代表的なECOを見てみます。

タスク 時間

------------- -------

マニュアル ECO 2-3日

STAR ECO 2-3時間

2. STAR-BUILDER—Verilog/VHDL RTLのストラクチャー検証

私たちは少なくともいくつかの問題を見つける事なしにRTLシミュレーションには至りません。

IPのストラクチャーが、全体のネットリストをシミュレーションすることなく正しく接続され

ている事を検証するためにSTARを使用することにより私たちは多くの時間を節約します。

以下は必要とする手順です:

1. 設計者はRTLネットリストとSTARに接続の観点から検証されるべきIPの

ストラクチャの仕様を入力する。

- IPのストラクチャの例:クロック、ロー・パワー、パドリング

2. STARは、そのストラクチャーのスタートとエンド・ポイントを自動的に

定義します。

3. 私たちの設計者は制約を指定し、STARに入力します。

- 例えば、私たちはストラクチャーの入力か出力に制約を持ちます。

適当な伝播の為の特定なバリューをセットするコンフィギューション・

レジスターのような。

4. STARは設計の階層とストラクチャーを通し制約を静的に伝播させること

によりストラクチャーの接続性を検証します。

- 例:パワー・モードかテスト・モードようにI/Oの制約がどこでブロ

ックされているかどうかを見る事

5. STARは、どのパスがブロックされ、何故ブロックが発生したかをユーザ

ーに示すための特別なGUIと検証レポートを持ちます。

- 例.マルチプレクサの設定ミス、私たちは、それをパスさせるために

信号を切り替える必要があります。

STARなしでデバッグするには、徹底的にテストを書く必要があります;時々1000の徹底的な

シミュレーションの検証を必要とします。

タスク 時間

------------------------------------ --------

STARによるストラクチャーの検証 数日

シミュレーションによるストラクチャーの検証 数週

図1.自動的に生成されたDefacto STARの接続ラッパーのコード

(CLICK ON PIC TO ENLARGE IMAGE.)

Defactoは、RTLが正しくて合成可能である事を保証するために独自の基本的なチェック機能を持

っています。一度それが完了すると、私たちは新しいRTLネットリストをCADENCE NC-Verilog

かVCSか ModelSimでシミュレーションを行います。また、DFTロジックの追加によってチップ

の機能が変化していない事を保証する為にDFTに関連した接続を生成する為にSTARを使用す

る場合、フォーマル検証(Conformal LECもしくはFormality)を実行します。

私たちは独自の追加ルールを作成するためにDefacto APIの使用ができます、もしくは、Defacto

の追加のストラクチャー検証のアプリケーションを使用できます。それについては後

で意見を述べます。

2. Design Exploration(設計の探求)

"Design exploration"はSTARの不可欠な基本部です--私たちはSynopsys DCがゲート・レ

ベルで探求するのと同様の方法でRTLを探求するのに使用します。

- 私たちはポートとインスタンスを見つけるために基本的なクエリ・コマ

ンドの実行することができます;そのサーチは本当に早いです--通常1秒

くらいです

- STARはまた、ファンイン、ファンアウトやパスのような先進的なフル・デ

ザインの階層のクエリをサポートしてます。

私たちはこの機能を随時使用します--われわれのRTL、アクセス、クエリなどを探求することがで

きることは非常に便利です。

3. ユーザー定義のデザイン・ルール・チェック(DRC)

私たちはRTLとゲート・レベルのパワーのチェックのためにSynopsys MVRCとCadence CLPのロ

ー・パワー設計ツールを使用してます。しかし、いつも早すぎて、EDAベンダーがまだサポートして

いないチェックを行います。

1.興味を持つ設計要素のトレースと定義をするためにSTARを使用します。

2.設計要素に適用するカスタム・デザイン・ルール・チェックを記述する

ためにTclとPerlを書きます。

例:

- ロー・パワー・ルール。ロー・パワー検証の為に、私たちはパワー・

スイッチ接続のためのDRCを実行します。これまでのところ、いつも

問題を見つけました。

- DFTルール。DFTの為の独自ルールを書くためにSTARを使用しますが、

高度なDFTルール・チェックには、DEFACTOのSign-off DFTルール・

チェッカーを使用します。

- メモリー接続チェック--すべてのメモリーが正しく接続されている事

を保証するために--特にロー・パワーとDFTに関係したすべてのポート

について。

4. Pin-to-Pinのトレース

私たちはクロック上の構造接続のチェックと長いシミュレーションをすることなしにI/Oマルチプ

レクサ・ロジックのために広範囲にSTARを使用します。主な目的は、制約のセットを適用した後、

2つのノードが構造的に接続されている事を保証する為です。

例:

- 特定のブロックの出力が特定のピンのマルチプレクサ・モードで

特定のチップI/Oに直接接続されている事。

- DFTのように特定のクロックが定義されたモードでPLLから特定の

ブロックの入力に伝播している事。

これらのpin-to-pinのトレース・チェック(制約下の)はたくさんの時間と労力を節約しま

す--特に妨害の位置を正確に示すことができるGUIで(もし、何かあれば)。私たちは、

その次のRTLが接続の意図を満たすことを保証するためのリグレッションとしてDefactoのチ

ェックを使用します。

---- ---- ---- ---- ---- ---- ----

STARの追加アプリ

Defacto STARプラットフォームは人々がiPhonesに機能を加えるのと同様の方法でユーザーによ

る拡張が可能です。モジュールもしくはアプリを追加します。私たちが現在使用しているいくつ

かはここにあります。

1. STAR-ECO—フルECOツール

STARは自動化されたECO機能を持ちます、IP自体のECOよりも、接続の追加と削除ような接続

の変更を主に行います。

STARのECOはRTLとゲート・レベルで動作しますが、私たちは主にゲート・レベルのECOのため

に使用 します。ゲートのセット追加をしたい場合、インバータのように、特定の方法で、私た

ちは特定タイプのネットのサーチやインバータの追加のためにSTARを使用します。手作業で

それを行う場合と比べてECOを行うために1つ(または少数の)のコマンド・ラインだけ

を必要とするだけです—新しいネットリスト加えるために手作業で階層を横断すること。

私たちはまたゲート・レベルでより複雑なECOを自動的に行うためにSTARを使用します:

- バッファをインバータに変更

- バッファのセットをインバータのセットに変更

- ANDゲートをNORゲートに変更

- フライでスキャン・チェーンをスティチィング;フロップの定義、

スキャン・チェーンの挿入、クロックの接続.

私たちのファンクショナルECOの多くは合成とLECを通します。合成の実行もしくは論理の等

価性のフォーマル・チェックの実行の必要性なしに自動的にゲート・レベルの変更行うために、

ときどき私たちはSTARを使用します。

例えば、私たちがロー・パワーの調整を行うとき:パワー・スイッチの接続、ISOセル

の接続、いろいろなアナログIP および/またはメモリーへのレベル・シフターの接続

とロー・パワー接続--フォーマル・ツールはれ自体、機能に影響をあたえないので変更

を見ることができません。Synopsysの Design Compilerはパワー・スイッチを知ること

も見ることもしません。DFTのECOについても同様です。変更はデバイスの機能には影響

しませんが、テスタビリティに影響を与えます。私たちはECOを実装するためにフォー

マルの方法は使用できません;その代わりにSTARを使用します。

私たちのSTARへの唯一の代替策は手作業でECOを行う事です。5階層の深さのノード

である場合、手作業による全てのポートの接続は苦痛です。

- 手作業によるECO:モジュールA、モジュールCなどを修正してからインター

フェースを変更し、ポートの追加しなければなりません。

- STARによるECO:1行だけ必要です。

STARは早いです。平均時間の節約のアイデアをあなたに与えるために、私たちの

代表的なECOを見てみます。

タスク 時間

------------- -------

マニュアル ECO 2-3日

STAR ECO 2-3時間

2. STAR-BUILDER—Verilog/VHDL RTLのストラクチャー検証

私たちは少なくともいくつかの問題を見つける事なしにRTLシミュレーションには至りません。

IPのストラクチャーが、全体のネットリストをシミュレーションすることなく正しく接続され

ている事を検証するためにSTARを使用することにより私たちは多くの時間を節約します。

以下は必要とする手順です:

1. 設計者はRTLネットリストとSTARに接続の観点から検証されるべきIPの

ストラクチャの仕様を入力する。

- IPのストラクチャの例:クロック、ロー・パワー、パドリング

2. STARは、そのストラクチャーのスタートとエンド・ポイントを自動的に

定義します。

3. 私たちの設計者は制約を指定し、STARに入力します。

- 例えば、私たちはストラクチャーの入力か出力に制約を持ちます。

適当な伝播の為の特定なバリューをセットするコンフィギューション・

レジスターのような。

4. STARは設計の階層とストラクチャーを通し制約を静的に伝播させること

によりストラクチャーの接続性を検証します。

- 例:パワー・モードかテスト・モードようにI/Oの制約がどこでブロ

ックされているかどうかを見る事

5. STARは、どのパスがブロックされ、何故ブロックが発生したかをユーザ

ーに示すための特別なGUIと検証レポートを持ちます。

- 例.マルチプレクサの設定ミス、私たちは、それをパスさせるために

信号を切り替える必要があります。

STARなしでデバッグするには、徹底的にテストを書く必要があります;時々1000の徹底的な

シミュレーションの検証を必要とします。

タスク 時間

------------------------------------ --------

STARによるストラクチャーの検証 数日

シミュレーションによるストラクチャーの検証 数週

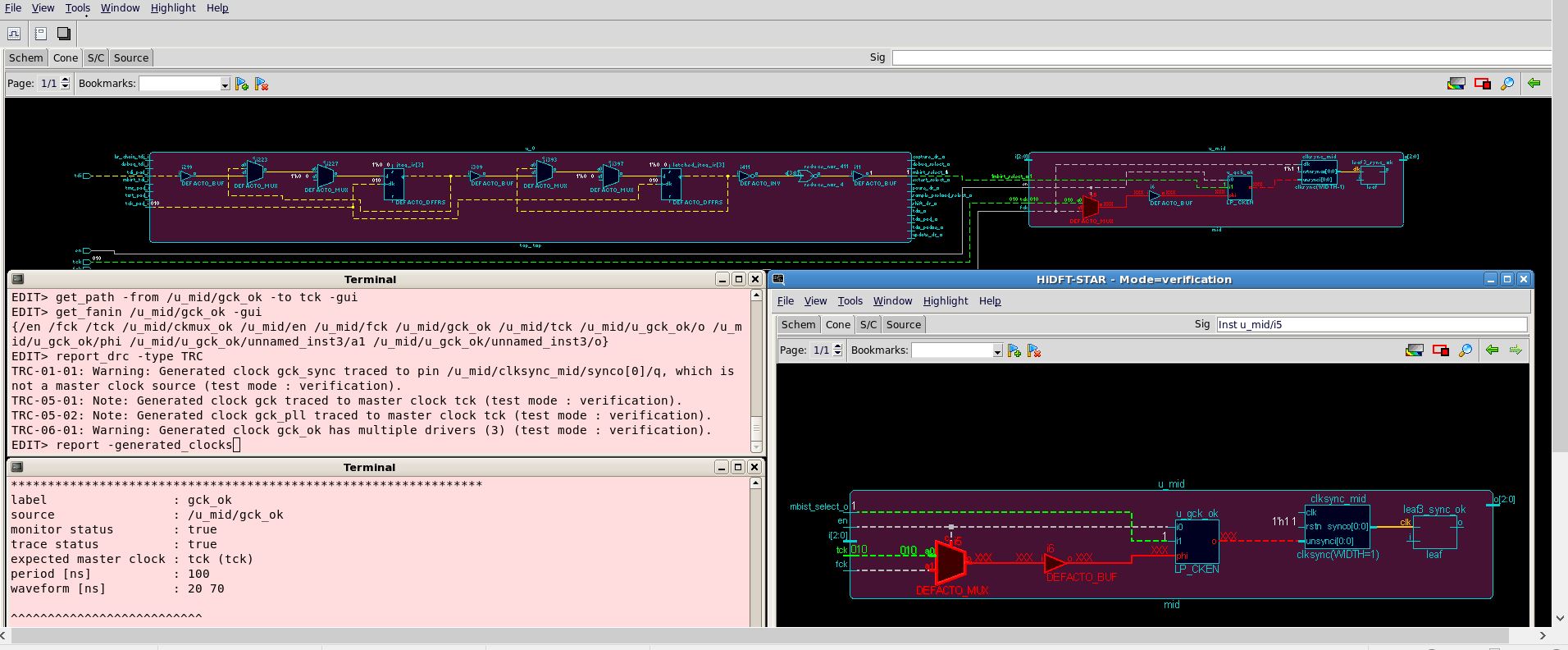

図2.クロックのストラクチャー検証の為のSTARのGUI赤のラインは障害となるパスのロ

ジック部をピンポイントで示します。下のグラフの0と1は何が間違えているかを示し

ます。 (CLICK ON PIC TO ENLARGE IMAGE.)

3. STAR-CK—クロックのテストベンチの生成

STARは単なる接続性を超えたより詳細な解析/シミュレーションのためのテスト・ベンチを生成できま

す。例えば、STARはクロックが正しいスピードで動作する為のテスト・ベンチを生成することができ

ます。私たちはこれを主に、検証する100のクロックがあるいろいろのDFTモードのクロックの検証

に使用します。

図2.クロックのストラクチャー検証の為のSTARのGUI赤のラインは障害となるパスのロ

ジック部をピンポイントで示します。下のグラフの0と1は何が間違えているかを示し

ます。 (CLICK ON PIC TO ENLARGE IMAGE.)

3. STAR-CK—クロックのテストベンチの生成

STARは単なる接続性を超えたより詳細な解析/シミュレーションのためのテスト・ベンチを生成できま

す。例えば、STARはクロックが正しいスピードで動作する為のテスト・ベンチを生成することができ

ます。私たちはこれを主に、検証する100のクロックがあるいろいろのDFTモードのクロックの検証

に使用します。

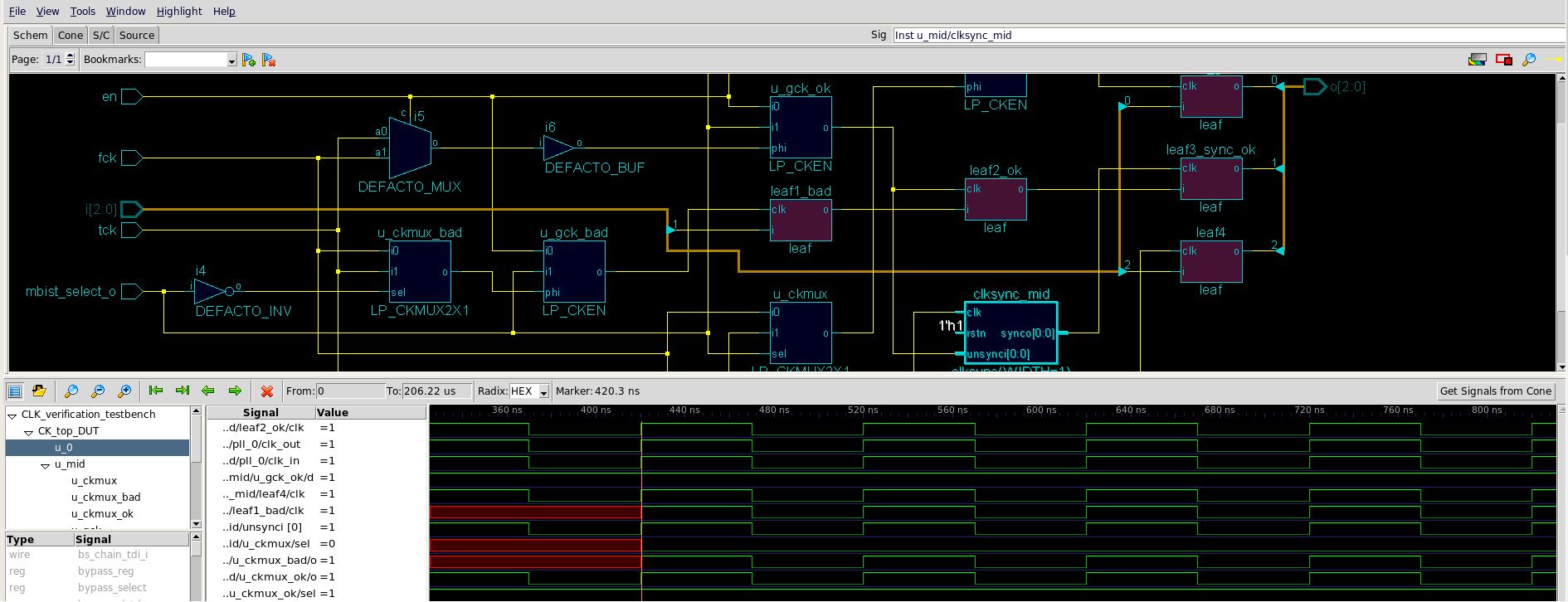

図3.STARが生成したテストベンチはシミュレーション前に解析することができます。

(CLICK ON PIC TO ENLARGE IMAGE.)

これの美点は、通常、ゲートで長いシミュレーションを実行する為のDFTの挿入工程まで待つこと

なしにRTLで早期に検証を行うことができます。

4. STAR-PADRING -- パッドリングの生成

STARの最新の追加アプリはパッドリングの生成機能です。それは、いつも複雑な問題でI/Oセグメ

ントにパワー・ドメインの導入により複雑になっています。STAR-Padringで数分で複雑なチップの完

全なパッドリングを生成することができます。それはいつもコレクト・バイ・コンストラクションです。

図3.STARが生成したテストベンチはシミュレーション前に解析することができます。

(CLICK ON PIC TO ENLARGE IMAGE.)

これの美点は、通常、ゲートで長いシミュレーションを実行する為のDFTの挿入工程まで待つこと

なしにRTLで早期に検証を行うことができます。

4. STAR-PADRING -- パッドリングの生成

STARの最新の追加アプリはパッドリングの生成機能です。それは、いつも複雑な問題でI/Oセグメ

ントにパワー・ドメインの導入により複雑になっています。STAR-Padringで数分で複雑なチップの完

全なパッドリングを生成することができます。それはいつもコレクト・バイ・コンストラクションです。

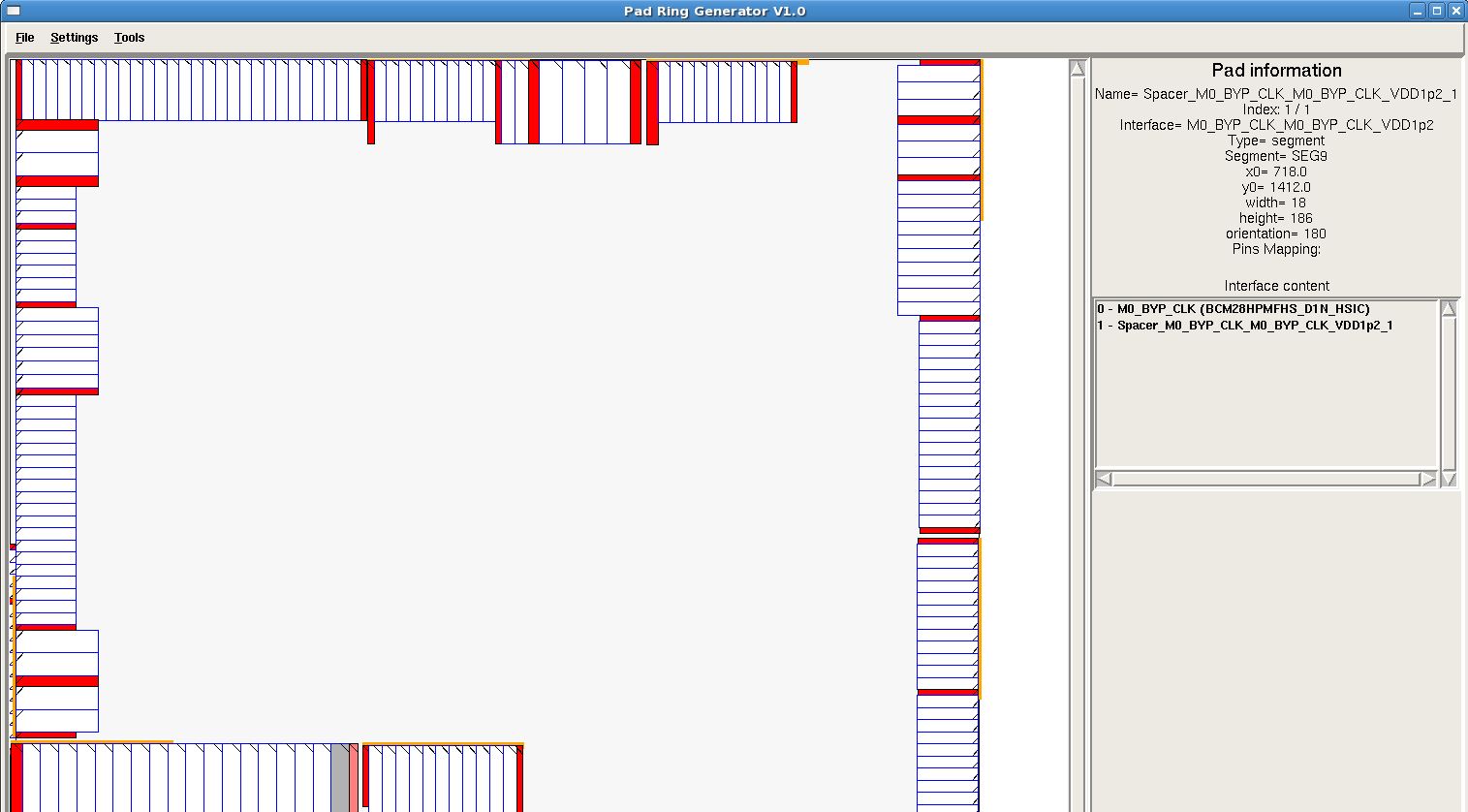

図4.パッドリングのRTLコード生成の為のSTARのGUI.正しいこと確認するための

自動デザイン・チェックとあわせて、再配置するパッドをドラッグ&ドロップ

できます。 (CLICK ON PIC TO ENLARGE IMAGE.)

STARは多様なパッドをサポートし、いろいろなパワー・セグメントに基づき対応したUPFを自動生成し

ます。設計者がチップのレイアウトの基づいたパッドを正しく配置すること支援するGUIを持ちます

。私たちはそれをテストした後、将来のデバイスに使用拡張することを望みます。

---- ---- ---- ---- ---- ---- ----

変更したいこと

DefactoのSTARに追加したい改善点:

1. 私はSign-off のRTL DFTルール・チェッカーをSTARに統合することを

依頼します。既にSTARで3-4の事項がなされ、行われることは良いです。

何故統合しないのかわかりません。それらは統合されるべきです。

2. Defactoがまだサポートしてない1つのことは'attributes'の概念です。

例.設計者のためのPost-its。それからIPの持つattribute/pointer/key

wordを入れることができた、その後、attributeのサーチでき、IPに

リンクできました。

3. STARアプリ・ライブラリーにもっとアプリを追加すること

私たちは、たくさんの内部のスクリプトを持っていました。それらは今やSTARにリプレースされ、

追加のユーティリティとして置き換えらました。開発時間を節約することに加えて、Defacto

は設計工程をより心配のない状態にしました。もし、従業員が退社したり職務変更の場合で

も--私たちはもはや回復できない大きな問題をもっていません。(これは実際に起こりまし

た)仕事に対処するために新しいエンジニアを雇ったとき、STARのクイック・トレーニングは、

コーディングを行っているチームの他の皆と同じ方法でコーディングを行う新人を持ったら

しました。当社の文化は設計に集中できるようDefactoのようなEDAにファンド提供するこ

とです。

それで私たちは適所にSTARを所有し、チームは毎日使用してます。1つのプラットフォームとし

て持つことを好みます、コマンドの1セットを学ぶだけで、ワン・ショットでそれらをするこ

とができます。時間の節約--IPの接続のための日数と検証のための週数-加算。さらに私にとっ

て心配事が少ない事です。何かがあった時に作業のために正しいツールを与えてくれるツール・

ボックスを自分のガレージに持つようなものです。

あなたが追加できるすべてのアプリを除いて、STARは,よりホームデポのようなものです。

- [ Asterix the Gaul ]

---- ---- ---- ---- ---- ---- ----

Editor's Note: This Japanese translation of ESNUG 530 #2 has been

provided by Shinji Iyobe of DSM Solutions in Shibuya, JP. - John

図4.パッドリングのRTLコード生成の為のSTARのGUI.正しいこと確認するための

自動デザイン・チェックとあわせて、再配置するパッドをドラッグ&ドロップ

できます。 (CLICK ON PIC TO ENLARGE IMAGE.)

STARは多様なパッドをサポートし、いろいろなパワー・セグメントに基づき対応したUPFを自動生成し

ます。設計者がチップのレイアウトの基づいたパッドを正しく配置すること支援するGUIを持ちます

。私たちはそれをテストした後、将来のデバイスに使用拡張することを望みます。

---- ---- ---- ---- ---- ---- ----

変更したいこと

DefactoのSTARに追加したい改善点:

1. 私はSign-off のRTL DFTルール・チェッカーをSTARに統合することを

依頼します。既にSTARで3-4の事項がなされ、行われることは良いです。

何故統合しないのかわかりません。それらは統合されるべきです。

2. Defactoがまだサポートしてない1つのことは'attributes'の概念です。

例.設計者のためのPost-its。それからIPの持つattribute/pointer/key

wordを入れることができた、その後、attributeのサーチでき、IPに

リンクできました。

3. STARアプリ・ライブラリーにもっとアプリを追加すること

私たちは、たくさんの内部のスクリプトを持っていました。それらは今やSTARにリプレースされ、

追加のユーティリティとして置き換えらました。開発時間を節約することに加えて、Defacto

は設計工程をより心配のない状態にしました。もし、従業員が退社したり職務変更の場合で

も--私たちはもはや回復できない大きな問題をもっていません。(これは実際に起こりまし

た)仕事に対処するために新しいエンジニアを雇ったとき、STARのクイック・トレーニングは、

コーディングを行っているチームの他の皆と同じ方法でコーディングを行う新人を持ったら

しました。当社の文化は設計に集中できるようDefactoのようなEDAにファンド提供するこ

とです。

それで私たちは適所にSTARを所有し、チームは毎日使用してます。1つのプラットフォームとし

て持つことを好みます、コマンドの1セットを学ぶだけで、ワン・ショットでそれらをするこ

とができます。時間の節約--IPの接続のための日数と検証のための週数-加算。さらに私にとっ

て心配事が少ない事です。何かがあった時に作業のために正しいツールを与えてくれるツール・

ボックスを自分のガレージに持つようなものです。

あなたが追加できるすべてのアプリを除いて、STARは,よりホームデポのようなものです。

- [ Asterix the Gaul ]

---- ---- ---- ---- ---- ---- ----

Editor's Note: This Japanese translation of ESNUG 530 #2 has been

provided by Shinji Iyobe of DSM Solutions in Shibuya, JP. - John

Join

Index

Next->Item

|

|