( ESNUG 535 Item 4 ) -------------------------------------------- [12/20/13]

Subject: Solido HSMC and Synopsys HSPICE to design a CMOS memory sense amp

> I was impressed with Solido's philosophy behind High Sigma Monte Carlo

> (HSMC), which is to "reach worst case quickly, and then search around

> worst case to derive that corner". Though it normally requires billions

> of samples to achieve 6 sigma confidence, it was interesting to see

> Solido get this with a few thousand samples instead.

>

> - from http://www.deepchip.com/items/dac13-04.html

From: [ Kenji Noda of NSCore ]

Hi, John,

My company, NSCore, is an IP vendor. We design non-volatile CMOS memories

at 180 to 65 nm.

We evaluated Solido's Variation Designer High Sigma Monte Carlo (HSMC)

product with our Synopsys HSPICE simulator. It only took us a half day to

get trained and set up with Solido HSMC, and we finished our evaluation by

the end of the 2nd day.

We've already purchased Solido's tool. I believe all memory designers

should use it.

We have to consider the retention characteristics of the OTP bit cells. The

signal of the memory bitcell gets smaller over time at high temperatures

like 125 or 150 degrees Celsius. We want our sense amps to sense that the

bitcell has a small signal; we must know the smallest signal our sense amp

can correctly sense.

---- ---- ---- ---- ---- ---- ----

METHODOLOGY BEFORE SOLIDO HSMC

We had issues designing to 6 sigma (1 x 10E9 samples) including sense amps

and our memory bitcells. For example, if we designed a bitcell for 5 sigma

(3.5 x 10E6 samples), then we had to consider the sense amps variation to:

2.7 sigma = 3 x 10E2 samples = (1 x 10E9) / (3.5 x 10E6)

Also, we need to simulate several different combinations of the variances

for our sense amps and bitcells.

Before we used Solido HSMC, we would just design, and then simulate with

Synopsys HSPICE to plus or minus 3 sigma for critical devices with the

worst-case bitcell model in 6 sigma variation. Our sense amplifier has

15 devices, and it was really difficult to define which devices were

critical and which weren't. With this method, we always underestimated

the performance of our sense amps.

For high sigma design, meaning anything above 4 sigma, it was simply not

feasible to do variation analysis with HSPICE alone. We would have had

to run millions or even billions of simulations.

---- ---- ---- ---- ---- ---- ----

METHODOLOGY WITH SOLIDO HSMC

Below is the methodology we use with Solido HSMC and Synopsys HSPICE, for

our 15-device sense amp.

1. We use the .MEASURE command in Synopsys HSPICE and compare the

voltage of 2 nodes.

2. We input the netlist into Solido HSMC, using Solido's command

line interface.

3. We specify the number of samples and the number of simulations

that we want Solido HSMC to run.

4. We run the read cycles for different dimensions and cells, which

either pass/fail. For example, if 10 points or 100 points fail

out of the 100's of millions or billions of samples that Solido

HSMC generates, then we know exactly what design yield is, i.e.

5 or 6 sigma.

5. If we find more failures than we expect, we can change the

dimensions on our sense amp. Solido has a text output which

identifies the problem transistors, along with suggested sizing

changes, so we know what to fix. This is a big help.

6. We design to a 95% confidence level for the specific sigma level

we set.

---- ---- ---- ---- ---- ---- ----

SOLIDO HIGH SIGMA MONTE CARLO RESULTS

Below is how Solido HSMC fared for speed, scalability, accuracy and

"verifiability".

1. Speed

Below are some Solido Variation Designer HSMC results for our test circuit

SIM_PB_SM sense amp and bit cells, with 15 transistors.

These were run using Solido HSMC and Synopsys HSPICE, with 4 CPUs. HSMC

verified the design at four different PVT corners.

Run time Failures/Total Sigma [Confidence

PVT Corner Min:Secs Samples Interval]

----------- -------- --------------- -----------------

#1: 3.3V/150C/SS 07:30 25/623 Million 5.306 [5.245-5.365]

#2: 2.3V/-40C/SS 07:35 217/623 Million 4.962 [4.936-4.988]

#3: 2.3V/150C/FF 07:50 13/623 Million 5.483 [5.388-5.578]

#4: 3.6V/150C/SS 41:03 37/10.1 Billion 5.783 [5.729-5.837]

As you can see, for corner #2, it took 7 min, 35 secs (= 455 seconds) for

1000 simulations, or .455 seconds per simulation, for Solido HSMC to verify

corner #2 to six sigma.

It is impossible to actually run Monte Carlo analysis to this level without

Solido. However, doing the math it would have taken us

.455 secs/simulation * 623,000,000 simulations = 8 years, 361 days.

We can even extract which sigma corners (3, 4, 5, 6...) to design to. For

example, if we want to design to 6 sigma, we extract the 6 sigma corners,

and then simulate against just those corners to ensure our entire design

will have a 6 sigma yield.

2. Scalability

HSMC makes designing to higher sigma feasible, due to the reduced number of

simulations required to get the desired accuracy.

Additionally, Solido claims HSMC can handle 10,000+ process variables. We

have only tested it up to 15-20 devices at the same time, with multiple

corners.

3. Accuracy

We assessed Solido HSMC's accuracy by viewing the number of failures

identified to ensure they looked reasonable. Because Solido uses HSPICE

simulation to identify each failure, we know there are no errors.

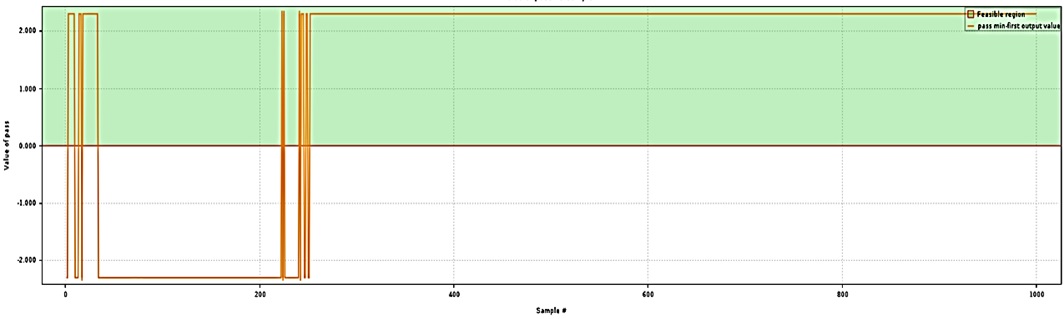

4. Verifiability

We are able to verify Solido's HSMC results using their convergence plot.

The way the Solido HSMC algorithmic works is to sort the samples from worst

to best, then simulate the worst samples first. Below is a sample of the

Solido Variation Designer convergence plot for our test circuit SIM_PB_SM

sense amp and bitcells. The circuit has a binary output.

Figure 1 below shows how in 1000 HSPICE simulations, HSMC demonstrated that

corner #2, with a supply voltage of 2.3V, -40 degree Celsius, and SS process

corner, is 4.962 sigma.

Fig 1) Distribution of Corner 2 (2.3V/-40C/SS) condition's

simulated samples. (Click pic to enlarge.)

217 failures / 623 million samples = 4.962 sigma

[confidence interval of 4.936-4.988]

In figure 2 below, a failure occurs at -2.3 V, while passing is +2.3 V.

Fig 1) Distribution of Corner 2 (2.3V/-40C/SS) condition's

simulated samples. (Click pic to enlarge.)

217 failures / 623 million samples = 4.962 sigma

[confidence interval of 4.936-4.988]

In figure 2 below, a failure occurs at -2.3 V, while passing is +2.3 V.

Fig 2) HSMC Convergence Plot, with ordered samples simulated

for corner 2. (Click pic to enlarge.)

As you can see, with Solido HSMC all the failure cases were discovered early

in the simulation process.

- All 217 failures were found in the first 270 ordered sample

simulations, out of the 1000 simulations and 623 million

samples we specified.

- It would have taken us 623 million simulations to find those

same 217 failures using a random Monte Carlo method.

Our automotive customers are very serious about accuracy. Without Solido's

HSMC, it would simply be impossible to accurately test the sensitivity of

our sense amp. We actually use Solido HSMC result to convince our customer

of our accuracy of our sense amps.

- Kenji Noda

NSCore, Inc. Fukuoka, Japan

Fig 2) HSMC Convergence Plot, with ordered samples simulated

for corner 2. (Click pic to enlarge.)

As you can see, with Solido HSMC all the failure cases were discovered early

in the simulation process.

- All 217 failures were found in the first 270 ordered sample

simulations, out of the 1000 simulations and 623 million

samples we specified.

- It would have taken us 623 million simulations to find those

same 217 failures using a random Monte Carlo method.

Our automotive customers are very serious about accuracy. Without Solido's

HSMC, it would simply be impossible to accurately test the sensitivity of

our sense amp. We actually use Solido HSMC result to convince our customer

of our accuracy of our sense amps.

- Kenji Noda

NSCore, Inc. Fukuoka, Japan

Join

Index

Next->Item

|

|