( ESNUG 546 Item 6 ) -------------------------------------------- [01/23/15]

Subject: Ellis on DesignCon, Allegro, HyperLynx, Ansys, Zuken, Micron, FPGAs

> Hi, John,

>

> I thought it was a clever idea by Luis Basto to write about some test

> topics 4 days right before the International Test Conference (ITC).

>

> In that vein, I'd like to share my ICCAD'13 Trip Report with you so

> your DeepChip CAD research readers would come to the ICCAD'14 that's

> coming up in 10 days.

>

> - Trent McConaghy, CTO

> Solido Design Automation Saskatoon, Canada

> http://www.deepchip.com/items/0538-14.html

Hi, John,

I thought I'd follow in this pattern and give your readers our

own internal DesignCon'14 Trip Report in anticipation of the

DesignCon'15 coming up next week. Our report focuses on FPGA's

because we sell FPGA and IP verification tools.

- Ellis Smith

Blue Pearl Software Santa Clara, CA

---- ---- ---- ---- ---- ---- ----

From: [ Ellis Smith of Blue Pearl ]

Here's the DesignCon attendance numbers for the past 5 years:

2010: ############################# 2,889

2011: #################################### 3,612

2012: ######################################### 4,151

2013: ############################################# 4,513

2014: ################################################ 4,750

It was held in the Santa Clara Convention Center on January 28-31, 2014.

Roughly 150 exhibitors had booths there with 18 being EDA or IP oriented.

Out of the EDA Big 3, only Cadence and Mentor showed. No Synopsys.

---- ---- ---- ---- ---- ---- ----

DesignCon Keynote: Eileen Bartholomew of the X Prize Foundation

Eileen delivered a truly inspirational speech. She started with the

hypothesis that companies and individuals need to take risk and not be

afraid of failure in order to "make possible what is thought impossible".

She continued by saying that right before a breakthrough, an idea is

still considered to be crazy. This happens because of the inflection

point inherent to a breakthrough since it is difficult to predict when

exactly it will happen.

The thought process should move from "local/linear" to "global/exponential"

in order to "prevent a Kodak moment".

She continued by saying that right before a breakthrough, an idea is

still considered to be crazy. This happens because of the inflection

point inherent to a breakthrough since it is difficult to predict when

exactly it will happen.

The thought process should move from "local/linear" to "global/exponential"

in order to "prevent a Kodak moment".

To explain the latter, she talked about how Instagram took over the Kodak

business in such a short time.

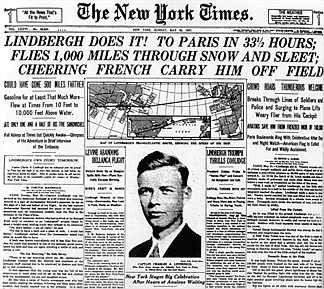

Then Eileen went to on explain the concept of crowd-based innovation and

prizes, which is the specialty of her company. She explained how XPIRZE

was motivated by Charles Lindberg's (the Flying Fool) solo flight from

New York to Paris for a $25K prize.

To explain the latter, she talked about how Instagram took over the Kodak

business in such a short time.

Then Eileen went to on explain the concept of crowd-based innovation and

prizes, which is the specialty of her company. She explained how XPIRZE

was motivated by Charles Lindberg's (the Flying Fool) solo flight from

New York to Paris for a $25K prize.

She added that this single contest created commercial aviation! Through

offering cash prizes, XPRIZE has prompted successes in Global Literacy,

Ocean Mapping, Carbon, Revolutionary Battery and Transporter.

---- ---- ---- ---- ---- ---- ----

DesignCon Keynote: Thomas Pawlowski of Micron Technology

Thomas' keynote focused on three topics related to chip memory:

- Micron Automata Processor,

- New Wall, and

- New Memory.

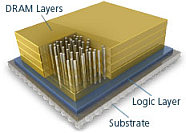

In "New Wall", he used the concept of throughput (concurrency/latency) to

refute the notion that we have a memory wall. And he spoke of the Micron's

Hybrid Memory Cube (HMC), which is a high-speed logic layer that sits below

vertical stacks of DRAM die connected using through-silicon-via's (TSV).

She added that this single contest created commercial aviation! Through

offering cash prizes, XPRIZE has prompted successes in Global Literacy,

Ocean Mapping, Carbon, Revolutionary Battery and Transporter.

---- ---- ---- ---- ---- ---- ----

DesignCon Keynote: Thomas Pawlowski of Micron Technology

Thomas' keynote focused on three topics related to chip memory:

- Micron Automata Processor,

- New Wall, and

- New Memory.

In "New Wall", he used the concept of throughput (concurrency/latency) to

refute the notion that we have a memory wall. And he spoke of the Micron's

Hybrid Memory Cube (HMC), which is a high-speed logic layer that sits below

vertical stacks of DRAM die connected using through-silicon-via's (TSV).

Eith companies are working on this: Altera, ARM, IBM, SK Hynix, Micron,

Open-Silicon, Samsung, and Xilinx.

In "New Memory", Thomas explained that memory abstraction needs to happen

(starting next year he predicts) due to technology scaling challenges and

the fact that memory is occupying more real estate on the chip.

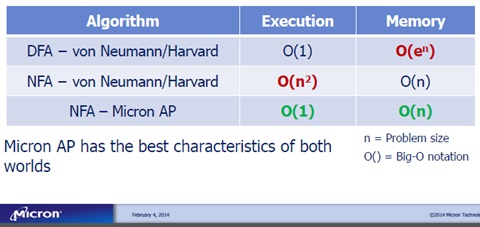

His Micron Automata Processor (MAP) talk generated significant interest

because its promised to tackle the world's most difficult compute problems.

Eith companies are working on this: Altera, ARM, IBM, SK Hynix, Micron,

Open-Silicon, Samsung, and Xilinx.

In "New Memory", Thomas explained that memory abstraction needs to happen

(starting next year he predicts) due to technology scaling challenges and

the fact that memory is occupying more real estate on the chip.

His Micron Automata Processor (MAP) talk generated significant interest

because its promised to tackle the world's most difficult compute problems.

The MAP is a memory-based processor with NO ALUs and NO opcodes, which

implements a non-deterministic state machine in silicon. He claims it is

Turing complete since it runs Conway's Game of Life. It is a massively

parallel processor which is ideal for unstructured problems.

The MAP is a memory-based processor with NO ALUs and NO opcodes, which

implements a non-deterministic state machine in silicon. He claims it is

Turing complete since it runs Conway's Game of Life. It is a massively

parallel processor which is ideal for unstructured problems.

The MAP is highly suited to solve graph problems like video/image analytics,

network activity and bioinformatics. Thomas sees 3 initial applications:

- Network security with millions of patterns,

- computational biology with large operands, and

- high perfomance computing for highly parallel operations.

ELLIS' ANALYSIS: We're personally excited about Micron's MAP method to use

graphs to model relationships. It fits well with our (Blue Pearl) symbolic

simulation tools. -- Ellis

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

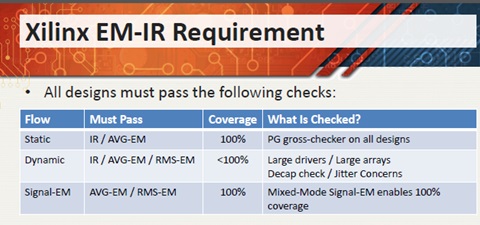

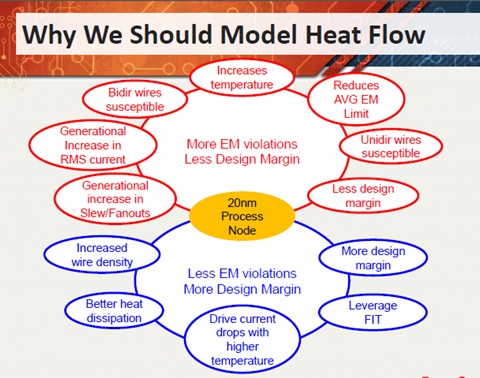

Paper: Comprehensive Full-Chip Methodology to Verify Electro-migration

and Dynamic Voltage Drop on High Performance 20 nm FPGA Designs

Authors: Sujeeth Udipi and Karan Sahni of Xilinx

The main theme was on the need for an integrated analysis, verification and

optimization methodology.

Sujeeth explained a typical Xilinx design is a mosaic of functional ties,

e.g. RAM, programmable logic, and IO tiles. He further said that Xilinx

verification designers are limited by the unavailability of a complete set

of vector for simulation purposes, by the fact that:

- the vectors come late in the design cycle, and

- that the vectors are manually generated, and

- they last for a limited duration.

On the other hand, Xilinx's EM-IR philosophy stipulates a 100% coverage,

"acceptable" accuracy and EM penalty paid within a fixed time interval.

He suggests a window slicing method for EM computation, but that average

EM violations can be waived if the design passes failure-in-time (FIT).

A fit of "1" indicates that the failure rate of the part will be 0.1% after

10 years.

The MAP is highly suited to solve graph problems like video/image analytics,

network activity and bioinformatics. Thomas sees 3 initial applications:

- Network security with millions of patterns,

- computational biology with large operands, and

- high perfomance computing for highly parallel operations.

ELLIS' ANALYSIS: We're personally excited about Micron's MAP method to use

graphs to model relationships. It fits well with our (Blue Pearl) symbolic

simulation tools. -- Ellis

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

Paper: Comprehensive Full-Chip Methodology to Verify Electro-migration

and Dynamic Voltage Drop on High Performance 20 nm FPGA Designs

Authors: Sujeeth Udipi and Karan Sahni of Xilinx

The main theme was on the need for an integrated analysis, verification and

optimization methodology.

Sujeeth explained a typical Xilinx design is a mosaic of functional ties,

e.g. RAM, programmable logic, and IO tiles. He further said that Xilinx

verification designers are limited by the unavailability of a complete set

of vector for simulation purposes, by the fact that:

- the vectors come late in the design cycle, and

- that the vectors are manually generated, and

- they last for a limited duration.

On the other hand, Xilinx's EM-IR philosophy stipulates a 100% coverage,

"acceptable" accuracy and EM penalty paid within a fixed time interval.

He suggests a window slicing method for EM computation, but that average

EM violations can be waived if the design passes failure-in-time (FIT).

A fit of "1" indicates that the failure rate of the part will be 0.1% after

10 years.

The Xilinx EM-IR corner is high temperature, nominal supply voltages, fast

transistors and extraction is typical.

Sujeeth then contrasted static vs. dynamic power EM-IR, and he looked at

the efficiency of decaps and suggested decap placement recommendation.

He then elaborated on a heat flow model where more EM violations lead to

temperature increases that cause increased slew -- which means less design

margin.

The Xilinx EM-IR corner is high temperature, nominal supply voltages, fast

transistors and extraction is typical.

Sujeeth then contrasted static vs. dynamic power EM-IR, and he looked at

the efficiency of decaps and suggested decap placement recommendation.

He then elaborated on a heat flow model where more EM violations lead to

temperature increases that cause increased slew -- which means less design

margin.

He also stipulates that EM is both dependent on peak current and slew rate.

Thus, proper verification need not only the vectors but also slew rates.

Moreover, Sujeeth pointed to the need for a divide-and-conquer approach to

perform full chip analysis. However, it is not easy to decide exactly where

to break the hierarchy.

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

Paper: An Implementor's Guide to Low Power

and High Performance Memory Systems

Authors: John Eble, Ming Li, and Wendem Beyene of Rambus

This was a paper focused on interface signaling and clocking, 3D packaging

and signal integrity analysis.

The presentation started by stating that it is relatively easier to achieve

speed as compared to low power. Memory interfaces are everywhere and

different system considerations (cost, performance, power, capacity, etc.)

lead to different device and systems considerations such as assemblies,

topologies and interfaces.

He also stipulates that EM is both dependent on peak current and slew rate.

Thus, proper verification need not only the vectors but also slew rates.

Moreover, Sujeeth pointed to the need for a divide-and-conquer approach to

perform full chip analysis. However, it is not easy to decide exactly where

to break the hierarchy.

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

Paper: An Implementor's Guide to Low Power

and High Performance Memory Systems

Authors: John Eble, Ming Li, and Wendem Beyene of Rambus

This was a paper focused on interface signaling and clocking, 3D packaging

and signal integrity analysis.

The presentation started by stating that it is relatively easier to achieve

speed as compared to low power. Memory interfaces are everywhere and

different system considerations (cost, performance, power, capacity, etc.)

lead to different device and systems considerations such as assemblies,

topologies and interfaces.

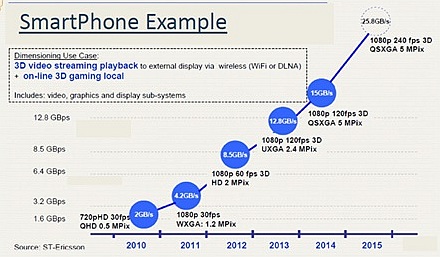

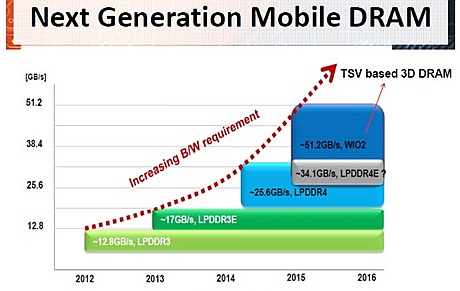

In mobile designs, the bandwidth requirement is growing exponentially due

to higher definition display, the need to achieve gaming performance level,

and the ability to display on monitors.

The authors claim it is no longer possible to achieve product requirements

with parallelism alone -- and that bandwidth-per-pin must increase.

In mobile designs, the bandwidth requirement is growing exponentially due

to higher definition display, the need to achieve gaming performance level,

and the ability to display on monitors.

The authors claim it is no longer possible to achieve product requirements

with parallelism alone -- and that bandwidth-per-pin must increase.

Moreover, virtually all designs have reached their critical power limits for

thermal dissipation, battery life and/or energy cost. Thus energy-per-bit

must be reduced to achieve the required higher bandwidth-per-pin!

One solution could be advanced packaging with wide IO and 3D integration.

There's active research on:

- using more equalization and crosstalk calibration

- low-swing signaling with RX offset calibration

- remove expensive local delay matching buffers

- faster wakeup times with zero idle power

- DVFS for slower dynamics and "drowsy" modes

In their interface signaling and clocking section, John said it is very

challenging to decrease DRAM core power since cell capacitance is nearly

constant to keep refresh times -- and process constraints like low leakage

dictate how low the voltage can be.

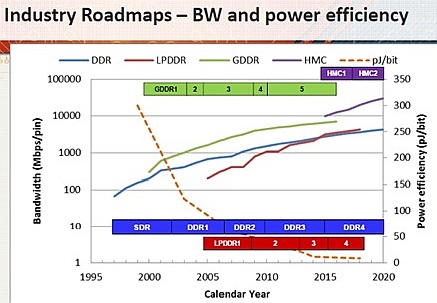

The two mainstream memory system topologies and types are DDR and LPDDR.

He noted that DDR has gone through 5 generations in 20 years, whereas

LPDDR has gone through 4 generations in about 8 years since mobile apps

are growing fast. Reducing power by two orders of magnitude requires

aggressive power states -- namely self-refresh, deep-power down, and

pre-fetch.

Moreover, virtually all designs have reached their critical power limits for

thermal dissipation, battery life and/or energy cost. Thus energy-per-bit

must be reduced to achieve the required higher bandwidth-per-pin!

One solution could be advanced packaging with wide IO and 3D integration.

There's active research on:

- using more equalization and crosstalk calibration

- low-swing signaling with RX offset calibration

- remove expensive local delay matching buffers

- faster wakeup times with zero idle power

- DVFS for slower dynamics and "drowsy" modes

In their interface signaling and clocking section, John said it is very

challenging to decrease DRAM core power since cell capacitance is nearly

constant to keep refresh times -- and process constraints like low leakage

dictate how low the voltage can be.

The two mainstream memory system topologies and types are DDR and LPDDR.

He noted that DDR has gone through 5 generations in 20 years, whereas

LPDDR has gone through 4 generations in about 8 years since mobile apps

are growing fast. Reducing power by two orders of magnitude requires

aggressive power states -- namely self-refresh, deep-power down, and

pre-fetch.

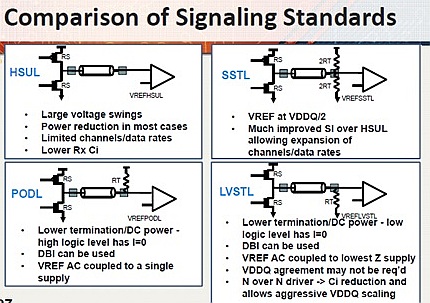

For mobile applications, the LPDDR interface is moving to LVSTL which allows

aggressive VDDq scaling. For high-speed signaling, we must treat channels

as transmission lines -- which means reflections, loss, and crosstalk.

During the system-level clocking section, John mentioned that DDR uses a DLL

to align strobe, data and clk. However, in LPDDR the DLL is foregone to

reduce power and wakeup time which means increased variability of read data

return and requires tracking.

Double-edge clocking may be a preferred compared to multi-phase clocks.

---- ---- ---- ---- ---- ---- ----

Ming talked about 3D packaging as a promising avenue to bandwidth and power

requirements.

For mobile applications, the LPDDR interface is moving to LVSTL which allows

aggressive VDDq scaling. For high-speed signaling, we must treat channels

as transmission lines -- which means reflections, loss, and crosstalk.

During the system-level clocking section, John mentioned that DDR uses a DLL

to align strobe, data and clk. However, in LPDDR the DLL is foregone to

reduce power and wakeup time which means increased variability of read data

return and requires tracking.

Double-edge clocking may be a preferred compared to multi-phase clocks.

---- ---- ---- ---- ---- ---- ----

Ming talked about 3D packaging as a promising avenue to bandwidth and power

requirements.

The industry is moving to TSV-based 3D memories, especially for mobile apps.

---- ---- ---- ---- ---- ---- ----

Wendem discussed how traditional SI analysis tools are insufficient due to

increased performance and reduce power; and as memory data rate skyrocket.

The industry is moving to TSV-based 3D memories, especially for mobile apps.

---- ---- ---- ---- ---- ---- ----

Wendem discussed how traditional SI analysis tools are insufficient due to

increased performance and reduce power; and as memory data rate skyrocket.

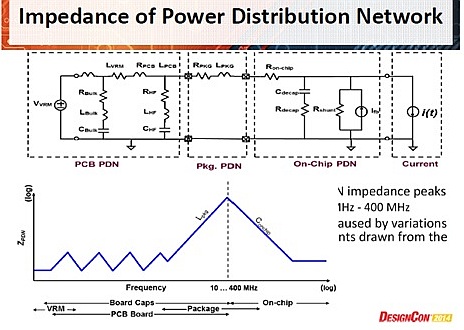

Bit-error-rate (BER) methods that consider a statistical distribution

of voltage and timing parameters become necessary. Power supply noise

introduces jitter, which in turn becomes a major source of timing

uncertainty. He argued that designers need to reduce power impedance,

and reduce peak power-distribution-network (PDN) impedance due to package.

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

EXHIBITORS AT DESIGNCON:

Mentor Graphics Corp:

Mentor was all about HyperLynx, their PCB analysis and verification software

suite. Leslie Vangrove and her team gave us a high level pitch about their

complete "spec" - to - "post-route" solution.

Their PCB 3D-EM product includes model extraction, support for modeling path

across package and board, especially transmission line.

Their PCB DRC solution was flexible to customize rules for EMI/EMC, signal

integrity and power integrity analysis. Designers can investigate physical

structures that are affected by radiation.

Their PCB thermal tool simulates conduction, convection and radiation and

produces thermal profiles to be used for overheating analysis. Their PCB

signal integrity does FastEye diagram analysis for 10 Gbit models.

Mentor's SERDES and DDR signoff methodologies using HyperLynx got quite some

attention. Their two DesignCon technical papers:

"The Jitter-Noise Duality and Anatomy of an Eye-Diagram"

and

"Computation of Time Domain Impedance Profile from S-Parameters"

were both well attended, and showed how Teledyne Lecroy was using Mentor's

PCB analysis tools in actual designs.

Cadence Design Systems:

Cadence showcased their Allegro/Sigrity PCB integration using a "great

alone, better together" slogan. (Cadence acquired Sigrity for $80 million

in July 2012.) Brad Griffin explained how the Allegro PCB technology is

used for first level constraints -- whereas more advanced signal integrity

and post-PCB-route analysis is done within Sigrity.

Bit-error-rate (BER) methods that consider a statistical distribution

of voltage and timing parameters become necessary. Power supply noise

introduces jitter, which in turn becomes a major source of timing

uncertainty. He argued that designers need to reduce power impedance,

and reduce peak power-distribution-network (PDN) impedance due to package.

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

EXHIBITORS AT DESIGNCON:

Mentor Graphics Corp:

Mentor was all about HyperLynx, their PCB analysis and verification software

suite. Leslie Vangrove and her team gave us a high level pitch about their

complete "spec" - to - "post-route" solution.

Their PCB 3D-EM product includes model extraction, support for modeling path

across package and board, especially transmission line.

Their PCB DRC solution was flexible to customize rules for EMI/EMC, signal

integrity and power integrity analysis. Designers can investigate physical

structures that are affected by radiation.

Their PCB thermal tool simulates conduction, convection and radiation and

produces thermal profiles to be used for overheating analysis. Their PCB

signal integrity does FastEye diagram analysis for 10 Gbit models.

Mentor's SERDES and DDR signoff methodologies using HyperLynx got quite some

attention. Their two DesignCon technical papers:

"The Jitter-Noise Duality and Anatomy of an Eye-Diagram"

and

"Computation of Time Domain Impedance Profile from S-Parameters"

were both well attended, and showed how Teledyne Lecroy was using Mentor's

PCB analysis tools in actual designs.

Cadence Design Systems:

Cadence showcased their Allegro/Sigrity PCB integration using a "great

alone, better together" slogan. (Cadence acquired Sigrity for $80 million

in July 2012.) Brad Griffin explained how the Allegro PCB technology is

used for first level constraints -- whereas more advanced signal integrity

and post-PCB-route analysis is done within Sigrity.

Extraction and analysis headaches become massive as your board clock speed

increases and PCB space decreases. Cadence demoed their signal integrity,

memory analysis, and high speed serial analysis tools to deal with this.

I must say that I found Cadence's high speed SERDES compliance checking

interesting. Since with DDR4 it is very difficult to get an eye diagram,

their demo showed how to check for tolerance. (The Cadence reps claim to

have compliance checking for PCI, HDMI and USB among others.)

This new Allegro-Sigrity integration is an interesting combination for their

PCB customers. Now CDNS users can make changes in Allegro and then run the

Sigrity SI analysis seamlessly inside Allegro to see how the changes affect

the overall board behavior.

EMA Design Automation

This Cadence OrCAD reseller for small and medium-size customers had their

Chris Banton announce TimingDesigner 9.3, their own add-on static timing

analysis tool. It now has hooks into Sigrity. They also showcased their

OrCAD library tool, EDAbuilder 3.0, which cam extract schematic symbol

library data directly from the PDF datasheet.

Ansys Apache:

Mark Ravenstahl demoed their SIwave which analyzes power integrity, signal

integrity and EMI of PCB and IC packages. Does DC voltage drop analysis

and automated decoupling capacitor optimization. They also showed their

Sentinel-TI doing thermal analysis of 3D stacked die.

For full custom IC designers, their layout-based electro-static discharge

(ESD) tool, PathFinder-D, received a DesignVision Award.

Altium

Showcased their PCB and FPGA tools doing ECAD/MCAD 3-D integration, FPGA

prototyping, design reuse, and ECO handling.

Nimbic

Raul Compansano's showed their nWave 3D field solver for power integrity and

EMI analysis of chip-package-PCB design. Also demoed using nWave SPICE

inside their own cloud. Mentor acquired Nimbic four months later at DAC'14.

Zuken

Griff Derryberry of Zuken and Hany Elhak of Synopsys demoed Zuken CR-8000 and

Synopsys HSPICE doing eye diagrams, auto reporting of setup/hold time,

derating, tVAC, and ringback violations board layout of a DDR3 SDRAM design.

CST of America, Inc.

Demoed their CST PCB STUDIO doing near- and far-end crosstalk, TDR, eye

diagrams, SPICE models, current flow on PCBs, packages, and interconnects.

Tektronix

Had their oscilloscopes, signal generators, logic analyzers, and protocol

analyzers do PCI Express compliance, DDR4 validation, 100G DataCom testing,

WiFi 802.11ac testing on live PCB boards.

CAST, Inc.

Showed IP for their own proprietary BA2 32-bit processors plus IP for 8-bit

ucontrollers, and H.264 video and image compression for FPGAs and ASICs.

Blue Pearl Software:

My company's tagline at DesignCon'14 was:

"Blue Pearl - IP and FPGA Verification. Automated. Before Debug."

We demoed how, from an HDL description, designers could run FPGA-centric

structural checks for Xilinx and Altera. As an example, we had our RTL

checks integrated inside the Xilinx UltraFast design methodology.

Extraction and analysis headaches become massive as your board clock speed

increases and PCB space decreases. Cadence demoed their signal integrity,

memory analysis, and high speed serial analysis tools to deal with this.

I must say that I found Cadence's high speed SERDES compliance checking

interesting. Since with DDR4 it is very difficult to get an eye diagram,

their demo showed how to check for tolerance. (The Cadence reps claim to

have compliance checking for PCI, HDMI and USB among others.)

This new Allegro-Sigrity integration is an interesting combination for their

PCB customers. Now CDNS users can make changes in Allegro and then run the

Sigrity SI analysis seamlessly inside Allegro to see how the changes affect

the overall board behavior.

EMA Design Automation

This Cadence OrCAD reseller for small and medium-size customers had their

Chris Banton announce TimingDesigner 9.3, their own add-on static timing

analysis tool. It now has hooks into Sigrity. They also showcased their

OrCAD library tool, EDAbuilder 3.0, which cam extract schematic symbol

library data directly from the PDF datasheet.

Ansys Apache:

Mark Ravenstahl demoed their SIwave which analyzes power integrity, signal

integrity and EMI of PCB and IC packages. Does DC voltage drop analysis

and automated decoupling capacitor optimization. They also showed their

Sentinel-TI doing thermal analysis of 3D stacked die.

For full custom IC designers, their layout-based electro-static discharge

(ESD) tool, PathFinder-D, received a DesignVision Award.

Altium

Showcased their PCB and FPGA tools doing ECAD/MCAD 3-D integration, FPGA

prototyping, design reuse, and ECO handling.

Nimbic

Raul Compansano's showed their nWave 3D field solver for power integrity and

EMI analysis of chip-package-PCB design. Also demoed using nWave SPICE

inside their own cloud. Mentor acquired Nimbic four months later at DAC'14.

Zuken

Griff Derryberry of Zuken and Hany Elhak of Synopsys demoed Zuken CR-8000 and

Synopsys HSPICE doing eye diagrams, auto reporting of setup/hold time,

derating, tVAC, and ringback violations board layout of a DDR3 SDRAM design.

CST of America, Inc.

Demoed their CST PCB STUDIO doing near- and far-end crosstalk, TDR, eye

diagrams, SPICE models, current flow on PCBs, packages, and interconnects.

Tektronix

Had their oscilloscopes, signal generators, logic analyzers, and protocol

analyzers do PCI Express compliance, DDR4 validation, 100G DataCom testing,

WiFi 802.11ac testing on live PCB boards.

CAST, Inc.

Showed IP for their own proprietary BA2 32-bit processors plus IP for 8-bit

ucontrollers, and H.264 video and image compression for FPGAs and ASICs.

Blue Pearl Software:

My company's tagline at DesignCon'14 was:

"Blue Pearl - IP and FPGA Verification. Automated. Before Debug."

We demoed how, from an HDL description, designers could run FPGA-centric

structural checks for Xilinx and Altera. As an example, we had our RTL

checks integrated inside the Xilinx UltraFast design methodology.

Our clock domain crossing (CDC) analysis includes checks through the

Xilinx CORE Generator and Altera MegaCore functions using Blue Pearl's

Grey Cell methodology. This enables finding CDCs that would otherwise be

missed if designers settled for a black box methodology.

We also automatically generate SDC timing constraints for downstream tools

from Xilinx, Altera, Cadence, Mentor, and Synopsys.

---- ---- ---- ---- ---- ---- ----

For us, DesignCon'14 was good. With close to 5,000 users attending and an

emphasis more towards PCB / IC package / FPGA, it hit a sweet spot for the

tools we sell. We'll certainly be at DesignCon 2015 next week.

- Ellis Smith,

Blue Pearl Software Santa Clara, CA

Our clock domain crossing (CDC) analysis includes checks through the

Xilinx CORE Generator and Altera MegaCore functions using Blue Pearl's

Grey Cell methodology. This enables finding CDCs that would otherwise be

missed if designers settled for a black box methodology.

We also automatically generate SDC timing constraints for downstream tools

from Xilinx, Altera, Cadence, Mentor, and Synopsys.

---- ---- ---- ---- ---- ---- ----

For us, DesignCon'14 was good. With close to 5,000 users attending and an

emphasis more towards PCB / IC package / FPGA, it hit a sweet spot for the

tools we sell. We'll certainly be at DesignCon 2015 next week.

- Ellis Smith,

Blue Pearl Software Santa Clara, CA

Join

Index

Next->Item

|

|