( ESNUG 578 Item 1 ) ---------------------------------------------- [12/01/17]

[ EDITOR'S NOTE: I love user critiques like this because it gives an

initial lay of the land -- plus one user's opinions about what's

good and what's not-worth-using in PSS tools. Cool! - John ]

Subject: Hands-on PSS user explains CDNS Perspec vs. Breker TrekSoC (pt 1)

THE PSS HORSERACE HAS BEGUN!: Talk about timing the news -- the week right

before DAC'17, the Accellera PSWG announced that *both* the Breker C++ and

the Cadence/Mentor DSL languages were going to be in the Portable Stimulus

Specification (PSS), thus finally kicking off a big ...

... 4-way PSS tool horserace and judging from the user comments -- RIGHT

NOW it has Cadence Perspec in 1st, Breker TrekSoC in 2nd, and Mentor InFact

in a very distant 4th... plus a mythical Synopsys Mystery PSS tool lingering

somewhere in a less distant 3rd place. (And no, not a typo. Mentor InFact

came in 4th place, *behind* Synopsys PSS, in this user survey.)

- from Cadence Perspec and Breker TrekSoC win #1 "Best of 2017"

From: [ Ant-Man, the Movie ]

Hi John,

I was glad to see users rate Portable Stimulus tools as #1 in your EDA tool

report this year. A few years ago we did an eval of Perspec vs. TrekSoC.

We settled on Perspec. Since it's timely, I thought I'd share what we saw

back then and now. Both tools have evolved since then, and I still use

and prefer Perspec.

Please note that since we went all in on Perspec, some of my Breker info

here might not be 100% current. If one of your other DeepChip readers could

correct this, it would help a lot.

Please keep my name and my company out of this, OK?

- [ Ant-Man, the Movie ]

---- ---- ---- ---- ---- ---- ----

A. PORTABLE STIMULUS OVERVIEW

The portable stimulus tools like Breker and Perspec automatically generate

your tests from the "use models" of your design under test.

- The PSS tools read in a description/use model of your design along

with the test intention and to create the tests.

- They also help find possible tests to generate -- which is of

especially high value when system is complex.

- The automation can save many man-months of effort, and reduce errors.

These PSS generated tests are in: C/C++ and/or SystemVerilog and/or SystemC

and/or Specman "e" (with UML/SysML and/or AMS planned to be added) -- and

since they are 'portable' across multiple verification tools like simulators,

emulators, prototypers, etc. -- they're called "portable stimulus". The

idea is you have to write your PSS only once and then you can re-use it

throughout your verification flow.

And once Accellera finalizes the Portable Stimulus Specification (PSS) in

2018, the idea is that you can then write test intent and code your use

model, and then use the same PSS across different EDA vendors.

---- ---- ---- ---- ---- ---- ----

B. PSS MODELING

There is an upfront investment to be able to use the portable stimulus tools

at the chip level.

To use PSS, you must break down your entire system into subsystems, such as

a graphic uP, DSP, modem, video display, peripherals, -- or in functional

systems like debug or coherency -- which are not limited to one IP.

You then model whatever you want to verify for your SoC. The model has the

actions, and the test is generated from combination of actions chosen.

The abstract models can be remapped to a new design structure, such as a

derivative design or IP block. The better the portable stimulus tool, the

more flexibility and portability it has.

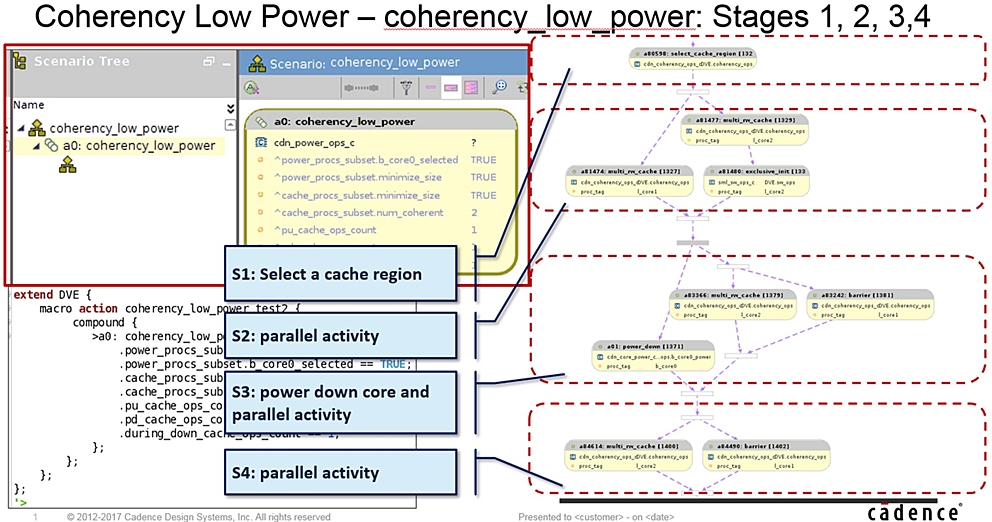

Cadence Perspec

With Perspec it is easy to divide your entire chip design space into

small subsystems.

Perspec uses libraries; you can build them yourself or use Cadence's

pre-built libraries.

- The libraries are a collection of low-level and high-level

actions.

- The input and output of each action of a subsystem and the use

cases between the actions are clearly defined.

- Users can customize a set of actions; then Perspec figures out

the possible inputs and outputs, and automatically builds the

tests for you.

You can use Perspec's SLN language to build your own library of

actions, which has native constructs and semantics to model

behaviors, including specific concurrent behaviors. SNL is tuned to

represent scenario spaces for hardware/software systems. You can

use SLN to represent:

- parallel and sequential execution

- loops and selections

- conditional branches

- data-flow and state pre/post-conditions

- resource pools

- resource claims

Perspec uses UML activity notation to represent various notions

graphically, with actions nodes and objects nodes, fork and join

nodes, decision and merge nodes, data-flow and control-flow edges,

and attributes and constraints.

(click on pic to enlarge image)

|

From what we saw, Perspec's text-based modeling doesn't have the

limitations of Breker's graph-based modeling. However, Perspec

still automatically generates a graph view so you can see what

you've done.

Memory management

Perspec also supports memory management. The way coherency works is

you must use a very small address range. Multiple processors must

choose a small portion of that range and share the same area.

Normally all that work would have to be done manually -- and that's

not very easy to do if you are writing test cases using 20-30

processors or 30-40 subsystems.

Cadence says they will align with the PSS DSL and C++ syntaxes once

it is approved.

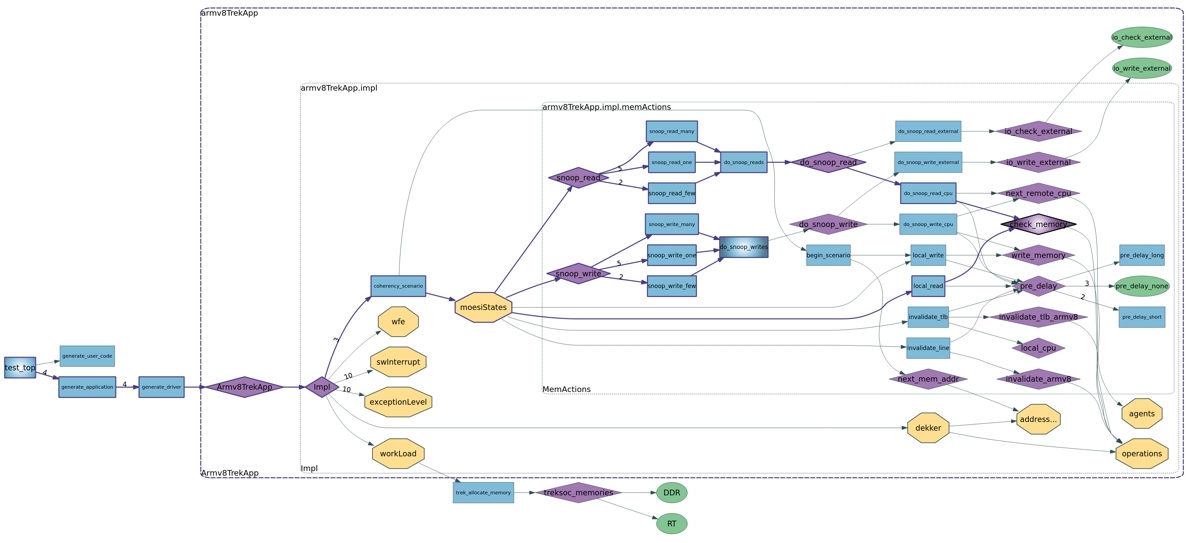

Breker TrekSoC

Breker initially used a Backus-Naur Form (BNF) notation. They now

support C++ and are expected to align with the coming PSS standard,

for both syntaxes.

(click on pic to enlarge image)

|

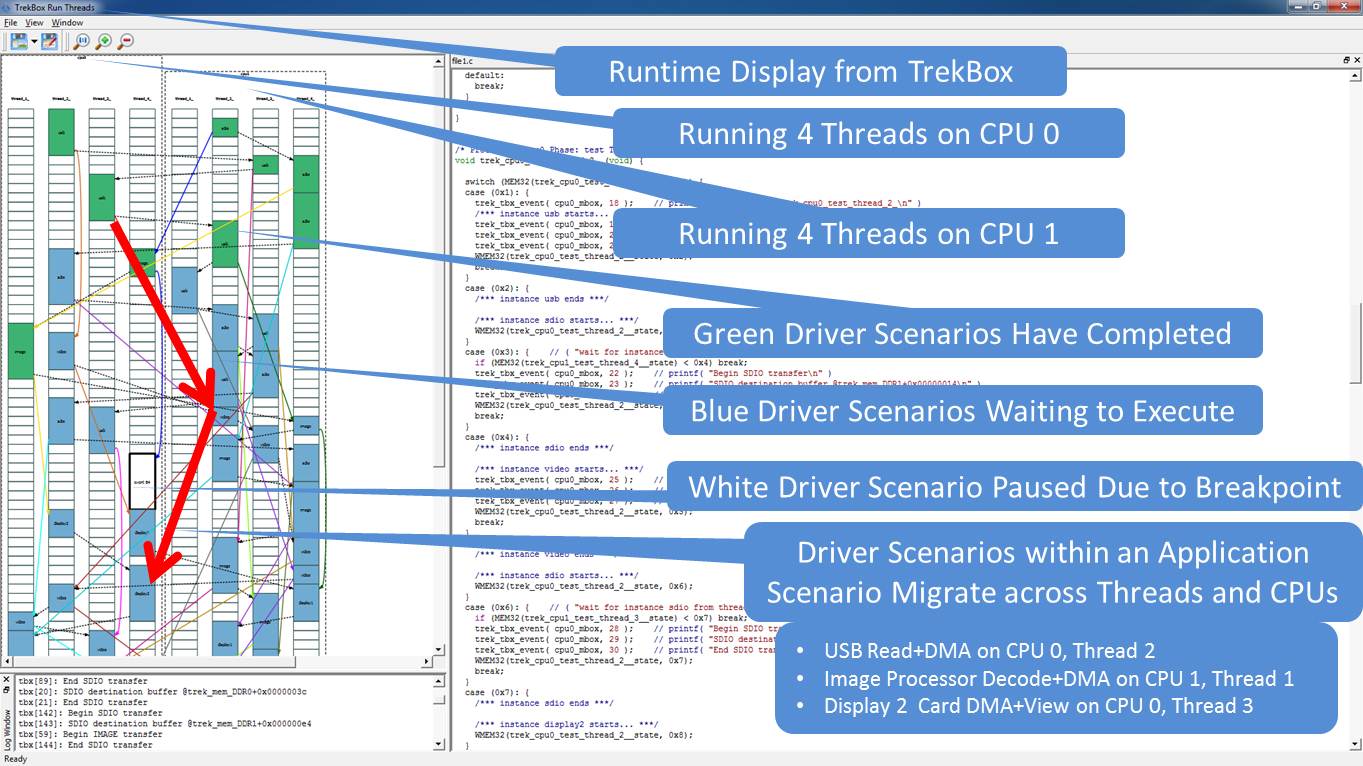

TrekSoC does portable stimulus modeling as a graph. Essentially you

take your overall SoC and describe it in flowchart-like graph bar.

Check out the image above to see how a graph looks. The image below

shows how a Breker graph is run in TrekSoC.

(click on pic to enlarge image)

|

A graph may work perfectly well for a small subsystem, or even with a

small SoC with very well-defined places for everything.

The drawbacks of Breker's graph approach for us were:

- It was very hard to use a graph to describe a system that

was very intertwined with lots of dependencies, such as

an SoC with 50 subsystems. For example, if you take a

PCI, that uses a certain kind of transport -- exactly how

is that PCI connected to a USB?

- It was hard to understand and maintain the graph.

Breker's graph method seems to be more of a legacy, as they started

out doing core-level verification. Breker then expanded from

verifying cores to verifying complex SOCs, but are still kind of

tied to their initial approach.

As with Perspec, you can build your own collection of actions for

TrekSoC or buy libraries -- though Breker calls them 'apps'.

Input and output of Breker actions are not clearly defined. Further,

interjecting interrupts and low power mode transitions adds yet

another layer/dimension of complexity to your Breker graph.

Memory management

Like Perspec, TrekSoC does memory management.

Breker's graph approach is essentially a model of sequential steps

and choices. They have ways for you to constrain the space of

choices for a given graph walk, and there are ways to compose larger

descriptions from smaller ones. However, unlike Perspec, their graph

language itself does not assign meaning to your steps and choices.

For me, Breker's graph approach was a very general way to capture a

space of possibilities; it just did not specifically represent our

test scenarios and test intent clearly.

---- ---- ---- ---- ---- ---- ----

C. PSS CONSTRAINT SOLVING

The PSS model can be viewed as set of constraints about the data flow in

your design, e.g. legal inputs and output types for an action.

As a result, portable stimulus tools have constraint solvers to generate

all the possible paths/tests. Doing it manually is not only time consuming,

but it's virtually impossible to see all the possible combinations. Plus,

design changes can invalidate some of the tests.

Cadence Perspec

With Perspec, you define the input and output types for all the

different actions. For an action requiring a certain input, the

tool then automatically solves (figures out) all the actions that

produce an output that can be consumed by that action.

Example: Actions A, B or C can produce an image, and action D can

receive an image. The Perspec constraint solver will automatically

determine that A, B, or C are input options for action D. The user

doesn't need to create these action connections.

Breker TrekSoC

You must specify all the possible connections in the graph yourself.

---- ---- ---- ---- ---- ---- ----

In part 2, I will cover PSS Test Intent, Libraries/Apps, and Debug.

- [ Ant-Man, the Movie ]

---- ---- ---- ---- ---- ---- ----

Related Articles

Hands-on PSS user explains CDNS Perspec vs. Breker TrekSoC (pt 1)

Hands-on PSS user explains CDNS Perspec vs. Breker TrekSoC (pt 2)

Hands-on PSS user explains CDNS Perspec vs. Breker TrekSoC (pt 3)

Cadence Perspec wins #1 in #1 "Best of 2017" with Portable Stimulus

Breker TrekSoC takes #2 in #1 "Best of 2017" with Portable Stimulus

Mentor InFact was pretty much an early No Show in the PSS tool wars

Join

Index

Next->Item

|

|