( ESNUG 586 Item 5 ) ---------------------------------------------- [04/23/19]

EDITOR'S NOTE: I soooo love scooping a story that was right in front of

everyone that the other "EDA press" missed! Nyah! Nyah! Nyah! - John

Subject: SCOOP! -- Anirudh goes total war on Ansys mothership at CDNlive'19!

I think we're seeing another chance for evolution right now with the

cloud. With Cloud, we ossified in a different... it was a new cathedral.

Which is, big companies have their own server farms and they put these,

someone was saying 'these design flows in place that work but they're

fragile and sacred and don't change them.'

And we can't use a new tool we better stick with friggin' RedHawk instead

of whatever the name'... the new one... GreenHawk. [audience laughter]

- Joe Costello, DAC'18 Troublemakers Panel (06/03/2018)

http://www.deepchip.com/items/0585-09.html

From: [John Cooley of DeepChip]

At first, CDNlive'19 was just like every other CDNlive. A big crowd shows

up and I'm lucky to find one of the last good seats up front so I can take

pics of the slides.

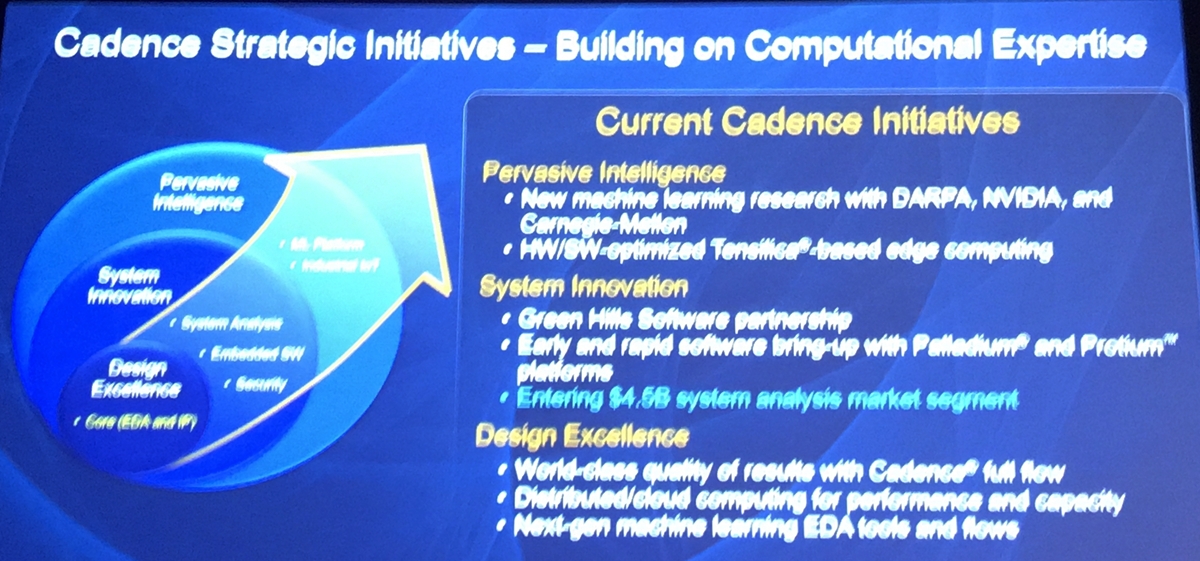

Lip-Bu gives a fairly standard State-of-the Union address about all things

cheery and good happening at Cadence. Data explosion. 71% CAGR. Video,

IoT, medical, automative, gaming, VR, robotics. ML/AI big driver for semi.

(click on pic to enlarge image)

|

Cloud, data center, edge, device. Strong design activity. Walden portfolio.

CDNS strategy to expand TAM from $10 billion to $30 billion. TenSilica.

PCB. Cadence CloudBurst. Palladium. Green Hills. new Clarity 3D Solver.

(and note that mention of "computational expertise" in the upper right.)

---- ---- ---- ---- ---- ---- ----

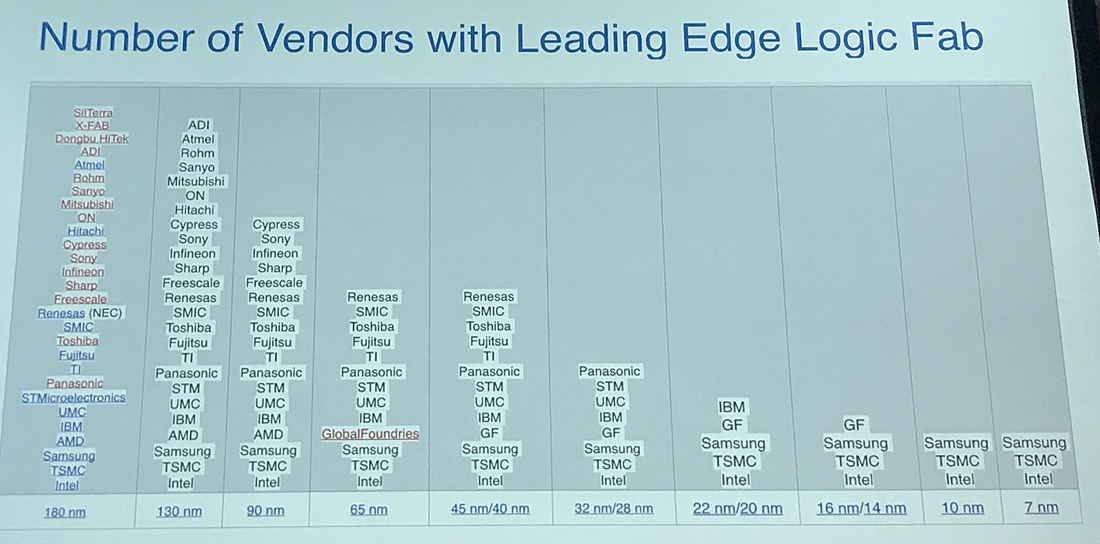

Then Andreas Maria Maximilian Freiherr von Mauchenheim genannt Bechtolsheim

(otherwise know as the "Andy Bechtolsheim", an early godfather to tiny

companies like Sun Microsystems, Cisco, Magma, Apache, and Real Intent) gave

a long talk about G5, Arista, and network speeds, etc. -- which went totally

over my head. But one slide he showed that I liked was:

(click on pic to enlarge image)

|

which, if updated, would only have TSMC and Samsung for 7nm. And at 5nm

and below who'll be left standing?

---- ---- ---- ---- ---- ---- ----

Then Anirudh steps up. He, of course, echoes some of what Lip-Bu had said

but goes deeper technically. blah blah (Innovus is kicking ass) blah blah

blah blah (Allegro PCB now has machine learning) blah blah (some exaggerated

Palladium/Protium lie) blah blah blah blah ... then the GOOD STUFF comes

up. Anirudh starts explaining his spiffy new Clarity 3D Solver!

(click on pic to enlarge image)

|

The money shot is Slide 16 (above). This is where Anirudh declared total

war on Ansys -- not the Apache division of ANSS -- but the ANSS mothership

itself. Of course, he never said the word Ansys nor Apache nor any of their

products by name, but I know a full out Declaration of War when I see one.

BACKGROUND: The Ansys mothership is multiple silos of computationally

similar tools mostly based on solving a mathematical matrix in a very quick

way -- sort of like how SPICE solvers work.

Wally Rhines taught this to me 21 years ago at DAC'99 when I asked him

"why does Mentor have Eldo SPICE?" His long detailed Wally-like answer

explained that "every flavor of SPICE is just a matrix being solved in a

slightly better and different way" -- which explained Eldo, HSIM, HSPICE,

FineSim, FineSim Pro, ProPlus, Silvaco, Keysight, Infinisim, Spectre,

BDA AFS, T-Spice, and Empyrean.

How Ansys makes it's money is by doing one type of matrix solution and then

applying that math across multiple vertical tool silos -- giving ANSS an

best-in-class operating profit margin of 43% to 45% -- because it's one time

R&D costs are then amortized over its electronics, semi, mil/aero, energy,

automotive, industrial, healthcare, consumer, and academic silos.

The other big plus is Ansys' HFSS finite element method (FEM) solver dates

back to 1989 and it's estimated to have 2,500 to 3,000 accounts worldwide;

a monster base to have. Depending on who you ask, the internal HFSS data

architecture dates back to the late 1990's -- it's a classic old school

single-threaded, non-distributed architecture... from ~20 years ago.

---- ---- ---- ---- ---- ---- ----

THE NIGHTMARE FOR ANSYS: It was all in Anirudh's Slide 16. He's launching

a 3D solver with structure-aware meshing. He said "totally new breakthough

algorithm" quite a few times -- meaning it's super fast. Then "the physics

does not change" -- meaning no approximations were involved; it's accurate!

(click on pic to enlarge image)

|

Then Anirudh spoke about his new *compact* data architecture designed from

the beginning to be auto-partitioned to run on a sea of cheap smaller memory

machines; plus it dynamically manages latency/fault-tolerance involved with

massive distributed computing on the cloud -- meaning it's high capacity!

|

Anirudh is attacking ...

|

|

|

And NOT attacking ...

|

|

And since his Clarity is finite element method (FEM) instead of a finite

integration technique (FIT), it was obvious to EM users I spoke with after

his keynote that he was NOT going frontal against 2nd place (Dassault) CST;

instead Anirudh was doing a full frontal assault on Ansys HFSS, the 1st

place 800 lb gorilla in EM solvers -- which is based a 20 year old single-

threaded, non-distributed data architecture that's a memory hog (meaning

you must hand segment larger designs), plus it's very NOT cloud friendly

(meaning each and every machine must have lots of cores and massive amounts

of memory to run it), plus HFSS lacks deep hooks into Cadence's Virtuoso

and Allegro.

From what I've heard, Cadence R&D has been directly working on Clarity for

about 18 months. But that short changes that Anirudh instituted a drastic

redesign of all CDNS data architectures back in 2012 to be compact and

distributed computing friendly.

So even if Ajei Gopal, the CEO of Ansys, sits down with his HFSS R&D group

today to deal with this Cadence threat, Ajei's guys won't realistically be

able to field a fully revamped cloud-friendly, compact data architecture,

massively parallel HFSS for at least 24 to 36 months -- and that's assuming

Ajei's guys make *no* mistakes in Operation HFSS Catch Up. Aart tried

this 4 years ago to no success (yet) with his IC Compiler 2 when Anirudh's

new data architecture/better algorithm Innovus attack came in -- and Aart

ended up -- after laying off 200 of his senior PnR R&D guys -- losing his

technical lead in digital PnR. (See DAC'18 #4b)

"You know, Aart will be lucky if he's in that mode in 2 years of

giving Anirudh's PnR job security a problem. Because we forget

sometimes, these are really hard problems and when you actually

pull together a team, you know a large team, with the diverse

skills to actually solve these problems -- you know it's not

quite a miracle -- but it's a work of art to make that happen.

And it's not a guarantee that you're going to be able to do it."

- Joe Costello, DAC'18 Troublemakers Panel (06/03/2018)

http://www.deepchip.com/items/0585-02.html

---- ---- ---- ---- ---- ---- ----

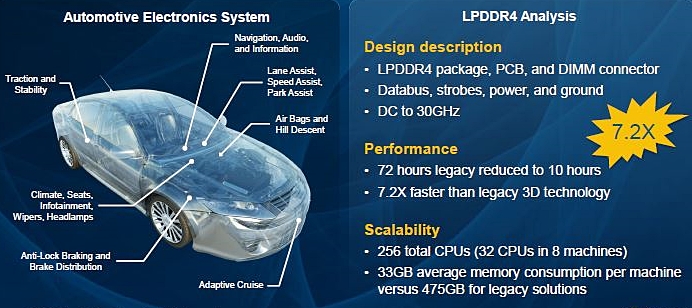

BENCHMARK DATA: All these glorious Clarity speed/accuracy/capacity claims

don't mean squat if you don't have the hard data to back it up. Anirudh's

next three slides in his talk were:

Right off, my first question: "what are the legacy tools in these slides?"

I was told that in all 3 benchmarks that "each user ran their legacy tool,

not any Cadence employees." (My guess also is Cadence could get into legal

trouble if they ran any rival's tool without permission.) (And then that

earlier FEM vs. FIT comment came up pretty much confirming to me that these

were 3 user-driven-HFSS vs. Cadence-driven-Clarity benchmarks run on the

user's own computer hardware.)

Show Me The Money: My next question was: "OK, so what's the comparative cost

savings of shorter runs that use less memory?". So assuming each project

took 6 months but that IT support effectively did a 2X on costs, I priced

out what buying a whole servers would be on Dell:

Dell 2 Xeon CPUs, @2.3GHz, 16 cores/processor, 2 processors

- 16 GB, 32 total cores sells for $9,900

- 32 GB, 32 total cores sells for $10,300

- 64 GB, 32 total cores sells for $10,700

- 128 GB, 32 total cores sells for $12,000

- 256 GB, 32 total cores sells for $15,100

- 512 GB, 32 total cores sells for $21,000

- 1.0 TB, 32 total cores sells for $40,000

- 1.5 TB, 32 total cores sells for $54,000

Benchmark #1:

(click on pic to enlarge image)

|

Ansys HFSS Cadence Clarity delta

---------- --------------- ---------

Total Runtime: 72.0 hrs 10.0 hrs 7.2X

Mem Per Machine: 475 GB 33 GB 14.4X

Machine used: 8 - 32 CPU 8 - 64 CPU

512 GB 32 GB

Total $ for machines: 8 x $21.0 K 8 x $10.7 K

= $168.0 K = $85.6 K 2.0X

NOTE: Mind you this only shows the impact of needing less memory. If costs

were prorated by hour (to account for using less runtime), Clarity using

10 hours would come out to be 14.4X cheaper than Ansys HFSS using 72 hours

in this benchmark.

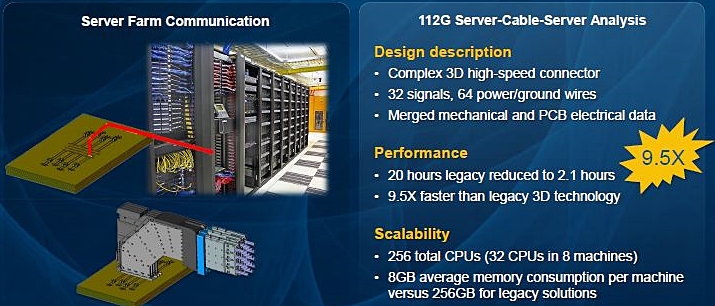

Benchmark #2:

(click on pic to enlarge image)

|

Ansys HFSS Cadence Clarity delta

---------- --------------- ---------

Total Runtime: 20.0 hrs 2.1 hrs 9.5X

Mem Per Machine: 256 GB 8 GB 32.0X

Machine used: 8 - 32 CPU 8 - 32 CPU

512 GB 16 GB

Total $ for machines: 8 x $21.0 K 8 x $9.9 K

= $168.0 K = $79.2 K 2.1X

NOTE: Mind you this only shows the impact of needing less memory. If costs

were prorated by hour (to account for using less runtime), Clarity using

2.1 hours would come out to be 19.9X cheaper than Ansys HFSS using 20 hours

in this benchmark.

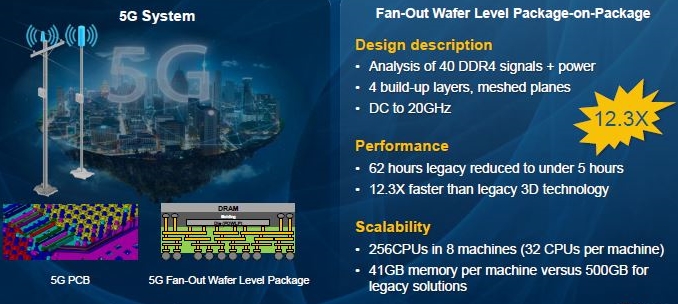

Benchmark #3:

(click on pic to enlarge image)

|

Ansys HFSS Cadence Clarity delta

---------- --------------- ---------

Total Runtime: 62.0 hrs 5.0 hrs 12.3X

Mem Per Machine: 500 GB 41 GB 12.2X

Machine used: 8 - 32 CPU 8 - 32 CPU

1.0 TB 64 GB

Total $ for machines: 8 x $40.0 K 8 x $10.7 K

= $320.0 K = $85.6 K 3.7X

NOTE: Mind you this only shows the impact of needing less memory. If costs

were prorated by hour (to account for using less runtime), Clarity using

5 hours would come out to be 45.5X cheaper than Ansys HFSS using 62 hours

in this benchmark.

---- ---- ---- ---- ---- ---- ----

THIS IS A SERIOUS THREAT: When you do 10X - 20x types of speed/memory/price

breakthroughs (like what Anirudh's showing here) -- that's when EM customers

comfortable with their olde reliable Ansys HFSS will sit up and take notice;

and even consider changing over to Clarity. Technically Clarity has/is:

- new compact data architecture -- uses 12x to 14x less memory

- cloud friendy -- manages latency & scalabiliy, fault tolerant

- new algorithm -- secret sauce that doesn't approximate physics

and is blazing fast

- deep hooks into Virtuoso/ADE and Allegro and Sigrity

- auto partitioned -- no segmenting needed!

- massive multi-threading, massively distributed

- uses many small cheaper and disparate machines, elastic compute

MASSIVE GROWTH FOR CADENCE: In business terms, this is a natural adjacency

for Cadence to grow into. Anirudh's R&D guys are all about tweaking and

improving and squeezing every last drop out of computationally intense EDA

problems -- jumping over to EM problems is a no brainer for them!

Depending on who you talk to, the TAM in EM simulation is $300M to $350M,

with HFSS owning 90% (or more) of the 3-D EM FEM sub niche. This new attack

by Anirudh is seriously bad news for Ajei Gopal -- because Ajei is stuck in

a defensive war with 20 year old classical single-threaded, non-distributed

data architecture and no Cloud. The best Ajei can do is throw FUD to buy

time, and try to minimize his loss in HFSS market share.

On the other side, this is all empty open green fields for Anirudh to grow

CDNS in. In the first 12 months he can take $10M away from HFSS, or $20M,

or $30M, or ... it's all pure growth for him. The only limit is how aggressive

his R&D guys are in making Clarity better than HFSS; and how aggressive his

marketing is in countering the FUD; and and how aggressive his sales guys are

in reaching the very entrenched Ansys HFSS customer base.

They could go Innovus (DAC'18 #4b) and kick ass.

Or they could go Pegasus (ESNUG 585 #1) and fall down.

We'll see.

- John Cooley

DeepChip.com Holliston, MA

---- ---- ---- ---- ---- ---- ----

Related Articles:

Anirudh and Sawicki on why CDNS and MENT did the Cloud this year

Costello dissecting Montana, Rocketick, Palladium, Zebu, Veloce

28nm vs. 7nm, AMS, Virtuoso, CDNS Innovus vs. SNPS IC Compiler 2

Costello on EDA ossification, cloud, and RedHawk vs. GreenHawk

Join

Index

Next->Item

|

|