( ESNUG 588 Item 7 ) ---------------------------------------------- [11/15/19]

[ Editor's Note: Within 3 hours of posting this, I had 4 different

engineers email me to say that "You misspelled RISC-V five times

as RISK-V." And, of course, all 4 were VERIFICATION engineers.

(And, YES, I corrected each of the spellings!!!! Grrr!) - John ]

Subject: Naveed and Costello discussing how SiFive/RISC-V will crush ARM

DAC'19 Troublemakers Panel in Las Vegas, NV

Cooley: Naveed. You may have noticed it that I made RISC-V number one

on my DAC'19 Cheesy Must-See list this morning.

Naveed: Thank you.

Cooley: But, if you also noticed in the write-up I said, I didn't say

you were going to make it. I didn't say that you're NOT going

to make it.

I just said, "Ask a lot of questions" -- and that every hardware

engineer should interrogate the hell out of you. [RISC-V]

Why do you, SiFive, have a chance against ARM?

Naveed: Okay, let me give you some numbers. So, in 3 years, we [SiFive]

have 70% of all the cores that ARM has -- in 3 years, the entire

portfolio.

In the last year and a half, we have 102 design wins.

Cooley: How many?

Naveed: 102.

[ Editor's Note: In same 18 months, ARM sold 188 new processor

licenses to their total 1,692 active legacy licenses. - John ]

Cooley: Okay, but how many are big ones versus, you know, oh wow, we

just took out a Cortex-M0.

|

|

Top 10 Semiconductor Vendors (2016 - 2018)

|

Naveed: If you look at the top 10 semiconductor companies, 6 of

them are engaged with us in a very significant way.

Cooley: Okay, define "significant".

Naveed: Significant means that they typically have a license, where you

can have all our RISC-V cores -- a very wide license for using

all the technology that we have.

That's what we mean by significant, not like 1-2 cores. That's

what I mean by that.

Cooley: Oh, so it's an All-You-Can-Eat type model.

When are we going to see a RISC-V chip inside the Apple X15?

Naveed: Apple X15? I don't know about that.

Cooley: I'm making up a future iPhone, you know...

Naveed: Ok, but I predict, in about 3 years, you will definitely see

RISC-V based cell phones. That will definitely happen.

Cooley: Okay. But is that like a Nokia candy bar phone?

Naveed: Well, you'll get to know about that... But my point is your

question was how can we [RISC-V] compete with some behemoth?

Cooley: Right, right.

Naveed: So let me answer you.

I think why people are adopting our RISC-V cores. Why do we

[SiFive] have so many designs wins (102) within such a short

time (18 months)?

I think the reason is very simple. Unlike somebody like ARM,

we at SiFive sell, not the core IP, but a reconfiguration tool.

You going to go to our SiFive portal, select a family, and then

you can dramatically modify that.

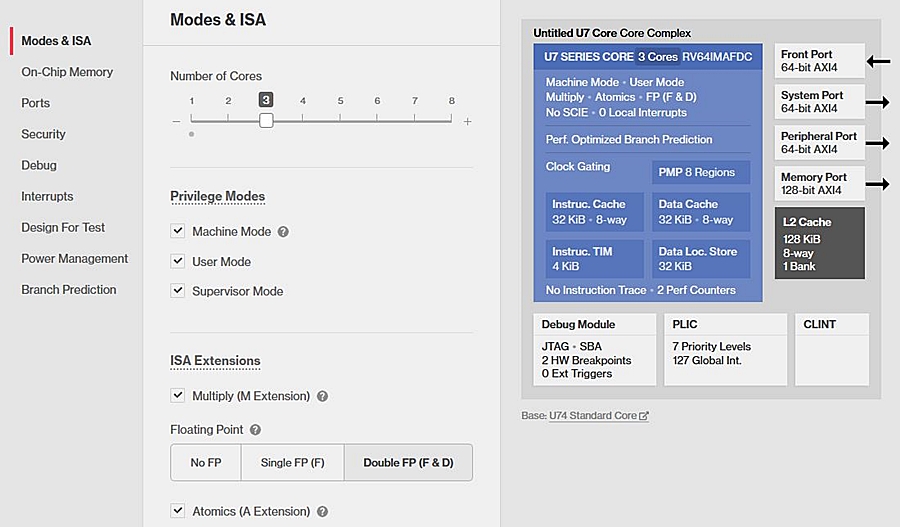

(click on pic to enlarge image)

|

And what I mean by dramatically modify the core is, for example,

with a click of a button you can drop a floating point unit.

You could drop a system port. Very soon, you will be able to

add vectors. You can switch between 32 and 64-bit architectures.

You could have for Edge chips, an extremely small microprocessor

with 64-bit with vectors on it. Things like that.

Cooley: Is that SiFive stuff an architectural exploration tool? What

pops out, hard IP? What's the end product?

Naveed: The end product is verified RTL.

Cooley: Okay. Then how do you do the synthesis and layout?

Naveed: We sell that as an IP. So, you get RTL (from SiFive), and then

you proceed with your own flow as though you had gotten RTL code

from somebody else.

Cooley: What about test -- verification and test? That's messy and ugly

and takes up 80% of chip design.

Naveed: Great. Let me come to that in a moment. But by doing what we

SiFive guys do, we can get dramatic results. What do we mean

by dramatic results? Some of our [SiFive] clients have told us

that they can get 1/3 the power on a similar [ARM] core.

Let me say that one more time. 1/3rd the power on a similar ARM

core.

Cooley: That's 1/3 off or 66% off?

Naveed: 66% off.

Cooley: Okay, so you're saying ARM is just really stupid?

Naveed: No. There's a lot of stuff in their [ARM's] core that is not

necessary for that application. They [ARM] have no ability

to take it out and we [SiFive] do.

So for any given core, the only stuff that you have for that

application is what you have. Everything else is taken out

because of the reconfiguration that we [SiFive] do.

Cooley: So, you're paring off the architectures is what you're doing?

Naveed: Yes.

Costello: But John, I think there's a bigger...

Pop it up to a slightly higher level about this trend about.

I think RISC-V is already a huge force, and it's only going

to grow.

We're taking tools and techniques and business models from other

sectors and markets that have been very successful. In this

case open source, and finally applying it in our sector.

There's no doubt. There's going to be way more investment ...

hardware and tool support around it [RISC-V]. Both software

tools for compilers etc. around it as well, as the hardware

tools and the flows that go with it.

Within a short period of time, I would predict within a year...

and some people say has already happened... you'd have to be an

idiot not to pick RISC-V as your platform for doing any kind of

custom processor work.

You would be foolish not to do it. It would be the same as

saying I'm going to do a new software project in a Cloud Native

way without using Kubernetes -- the same kind of silliness.

It's a fundamental movement and the force behind it [RISC-V],

the investment behind it, in software, in hardware, and the

tools that go with it, and the number of people working on it.

And there are multiple RISC-V versions. There's a SiFive

version of it, where people are taking the cores from

SiFive and doing their own thing.

That's what's going to make RISC-V, you know, a super important

movement and the custom processor movement is the foundational

movement of the next decade. That's what's going to change the

whole IC world for us. And RISC-V is right at the center, with

the most momentum behind it.

Cooley: Okay. I'll be an engineer here.

I want to know the cost differential. If I have an ARM core,

and I have a IISK-V core -- or a SiFive RISC-V core -- what's

the price difference?

Costello: I think one is free. [laughter]

Cooley: That's what my boss will ask me.

Naveed: I think the typical cost, if you take the total overall cost,

SiFive would be less than half of ARM for sure. And in some

cases, much less than that.

Cooley: Do you [SiFive] do royalties?

Naveed: Depending on what the customer wants, but typically we don't.

Cooley: Okay, but you're saying [SiFive is] half the cost, maybe

royalties, maybe not.

Naveed: And sometimes much less than half.

Cooley: Much less than half?

Naveed: Yes.

Cooley: Okay.

Naveed: The reason is as follows ... unlike the other situation, where

somebody [ARM] has a hold on the architecture, we [RISC-V] don't.

If we [SiFive] charge too much, the customers will do RISC-V

themselves. So there is a natural balance.

So we at SiFive have to find a price point that we can charge

before tipping it. If we tip it, the customers says "okay screw

you. I'm going to do RISC-V myself."

This is an automatic price control because of RISC-V being

Open Source.

So, as a result, we at SiFive can never raise our prices or

blackmail our customers, where others [ARM] can.

Costello: And look John, [Metrics/Montana] is a small company using the

RISC-V core.

We're getting essentially an architectural license, and we

don't pay anything for it, and we can use it to do anything.

Mo: So, as I guess as one of the chip designers on this panel, one

of the things that I see is that "it's the ecosystem".

I have friends and customers who are using RISC-V, and it's

just not the architecture.

It's what SiFive is putting together in terms of the ecosystem,

which you know, I think is part of the experience as well.

That's how I see it from our perspective.

Cooley: Alright.

---- ---- ---- ---- ---- ---- ----

Related Articles:

Naveed and Costello discussing how SiFive/RISC-V will crush ARM

Raik on OneSpin's four formal technologies the others don't have

Costello on Metrics cloud Verilog is at right place, right time

Join

Index

Next->Item

|

|