( ESNUG 588 Item 20 ) --------------------------------------------- [07/24/20]

Subject: User benchmark has "new" AFS-XT at 3x to 11x faster than Spectre-X

Well, spies tell me that Anirudh's using this exact same solver technology

to give his elderly Spectre SPICE franchise a big dose of the BLUE PILL.

Yes, grandpappy Spectre is now a hot new young virile Spectre-X that's:

- massively parallel (runs up to 128 CPUs)

- new compact data model (5X smaller than present day Spectre)

- super fast (up to 10X faster than present day Spectre)

- 100% backwards compatible to present day Spectre/APS/RF/XPS/AMS

This new Cadence Spectre-X is Full SPICE accurate -- that is it's NOT

Fast SPICE, it's Full SPICE.

- from Anirudh is launching a new Spectre-X SPICE at this DAC'19

RAVI COUNTERATTACKS SPECTRE-X: Last year at the In-Person DAC'19 Anirudh

ambushed Ravi Subramanian's MENT BDA AFS SPICE empire when Anirudh launched

his own new 4x to 30x faster Spectre-X.

At the time, I cited how Spectre-X impacted Aart's many SPICE's, but don't

be mislead -- Anirudh's true target was BDA AFS -- because BDA AFS is the

only true *technical* threat to Spectre. Aart & Anirudh often sell their

SPICEs based on package deals. "Hey, since we're buying a ton of Virtuoso

(or PrimeTime) licenses anyway, how much if you throw in a mess of Spectre

(or HSPICE) licenses to sweeten the deal?" While BDA AFS has to make sales

based purely on it being waaaay better than CDNS/SNPS SPICEs to justify the

added costs -- plus the added hassle of dealing with yet-another-EDA-vendor.

So each time when AFS proves itself to actually be better, Anirudh (& Aart)

both lose sales and lose face.

---- ---- ---- ---- ---- ---- ----

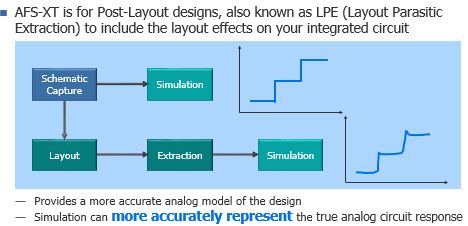

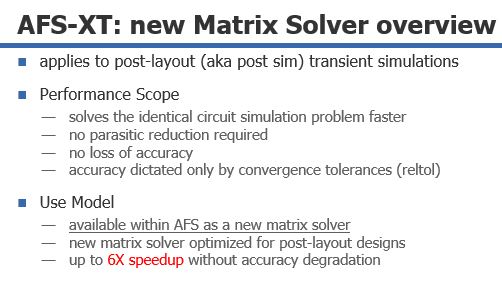

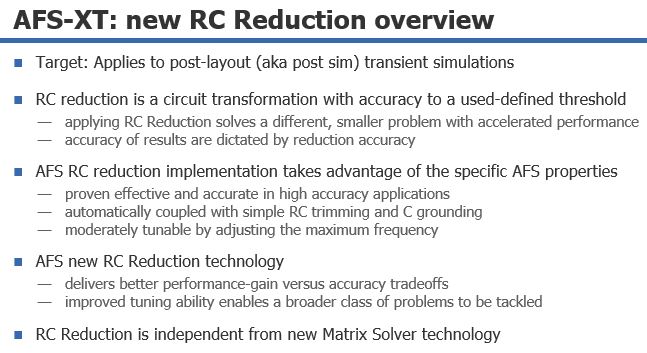

DETAILS SAY IT EVEN MORE: After I got the tech briefing from the MENT folks,

it was even more obvious how AFS-XT is an anti-Spectre-X attack. In a

nutshell, Ravi claims his new AFS-XT has:

- a new adaptive matrix solver <-- just like Anirudh

- a new added RC reduction <-- just like Anirudh

But

- only needs 16 CPU cores <-- Anirudh uses 256 or more CPUs

- better bsim evaluation <-- does Anirudh have this?

- heuristic time-step control <-- Anirudh does NOT have this!

And the truly crazy thing is ...

- AFS-XT is a *free* upgrade! <-- WTF? Anirudh doesn't do free!

The executive summary on the MENT technical slide shows all this.

Plus the other slides back it up.

(click on pic to enlarge image)

|

(click on pic to enlarge image)

|

(click on pic to enlarge image)

|

(click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

NOW A USER BENCHMARK

After that tech briefing w/ the MENT folks, as is my custom to check this

out I did a deep dive with an anonymous hands-on SPICE-using engineer who

was benchmarking AFS vs. AFS-XT.

He confirmed:

- Compared with AFS, AFS-XT gave us a typical 2X to 11X speedup

for post-layout simulations while maintaining accuracy.

- Yes, AFS-XT has a:

new adaptive matrix solver

new RC reduction algorithm

- These AFS-XT 2x to 11x speed-ups only apply to post-layout

simulations. Pre-layout runs do NOT get a speed-up. Old AFS

and AFS-XT run the same speed on pre-layout designs.

- "What's impressive is Mentor is not charging any additional

license fee to use AFS-XT along with your AFS licenses."

And here's his AFS vs. AFS-XT data in his own words.

From: [ An Anon SPICE User ]

To: John Cooley of DeepChip.com

Hi, John,

We benched 6 designs; 5 gave us non-outlier data. Here's the relative

speed-up we saw of AFS-XT compared to standard AFS.

LC-VCO (7nm): :###################### 10.9x faster

PLL locking (7nm): :###### 2.9x

VCO (7nm): :######### 4.3x

VCO (16nm): :####################### 11.5x

charge pump (16nm): :####################### 11.3x

This averaged to AFS-XT being 8.2x faster than the old AFS

But John, before I give you the details behind my benchmarks, I need to

explain why we need the fastest-yet-accurate SPICE available.

---- ---- ---- ---- ---- ---- ----

POST-LAYOUT SPICE RUNS ARE NOW MANDATORY

We used to be able to run SPICE on our schematics and then later run a

post-layout SPICE for sign-off -- and the simulation results would be

similar. However, at 16nm and below FinFET nodes, the number of R & C

parasitics grew very large -- and the value of those parasitics become

significant relative to the MOS devices' intrinsic Rs & Cs.

At 16nm, we get large discrepancies between our pre-layout (schematic)

results and post-layout results (and it's especially bad at 7nm and

below). We see big differences in key circuit measurements such as jitter,

phase noise, or SNDR between pre-layout and post-layout simulations.

Our new religion at 16nm became the LAYOUT is now the CIRCUIT. Never

count on a pre-layout view to get any confidence about your silicon.

Now, at/below 16nm, schematic sims only verify *general* functionality;

and they do NOT verify the design's performance. We now must extract the

layout parasitics and simulate the post-layout version to know exactly

how our circuits will behave.

Unfortunately, the SPICE simulation time increase is so huge that it is

becoming impractical. We've seen 5 to 6 day runs for 7nm post-layout

fractional-N PLL and SerDes circuits. And we need to continue these

post-layout sims even after we tapeout -- which is a royal pain while

we wait for the chip to come back because these sims are too long to

run and there are too many to run.

Since now "the layout is the circuit", then we also need to run all the

BSIM device parameter variation simulations (using the BSIM device model

equations) across a flood of process, voltage, and temperature (PVT)

points on the post layout view to characterize the circuit.

So suddenly we are faced with an angry sea of newly required post-layout

simulations -- but not a whole lot of time in which to do them.

From our company stats, moving from 10nm to 7nm to 5nm we have faced

a 9x increase in the number of simulations required at each node to

accurately characterize a performance-critical circuit.

---- ---- ---- ---- ---- ---- ----

To show this parasitics-driven explosion in runtime, below I have

5nm old AFS (not new AFS-XT) runtime comparisons across six modes:

- AFS modes 2 & 3 have traditional RC reduction on by default

- AFS mode 4 is AFS's out-of-the-box default setting

- AFS mode 6 is the highest accuracy (and longest runtime)

The relative runtime comparisons are between:

- Schematics (Sch) is pre-layout

- Coupled Capacitances (CC) extracting capacitance only

- Resistance & Capacitance (RC) extracts both

It's a 5nm ring oscillator VCO. Simulations were run for each afsmode

(accuracy) setting, for each of the three netlists (schematic,

CC-extracted, RC-extracted).

The first plot (above) is scaled relative to afsmode=2 (i.e. our 1X on

y-scale is at afsmode=2) of a Sch netlist. It shows that post-layout

simulations are 3x to 16x times slower than pre-layout simulations, and

at afsmode=6 (when you get the highest accuracy), post-layout can be

16x slower than pre-layout. Ouch!

This second plot (above) has the same data, but is scaled relative to

"1X being afsmode=4 (default out-of-the-box setting) of a sch netlist"

and we can still see the same large penalties for running RC extracted

post-layout simulations (in this case, up to 26x slower).

We say every simulator is dog slow if you need an accurate result with

an extracted netlist. We now live with the fact that post-layout sims

are ridiculously long -- but they are mandatory for everyone now.

This is why we need the fastest-yet-accurate SPICE available.

---- ---- ---- ---- ---- ---- ----

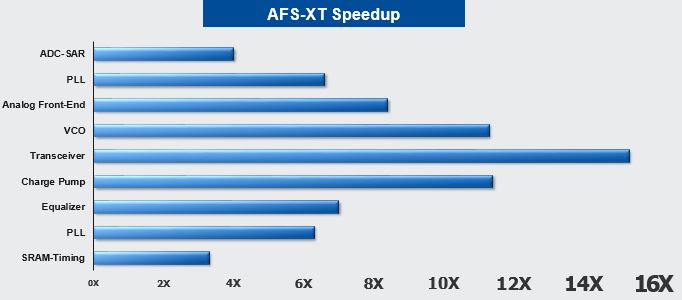

OUR AFS-XT BENCHMARK DETAILS

All were on on post-layout extracted clocking circuit IP (e.g. PLLs).

Settings definitions were:

AFS = default old out-of-box reference AFS (no AFS-XT)

AFS-XT "red" = new AFS-XT matrix solver only

AFS-XT "green" = new AFS XT solver + new AFS XT RC reduction

The "green" was "--parasitics 1e12" with a 1 THz cut-off.

To summarize the new AFS-XT speedup results over old AFS:

AFS-XT "red" (solver only): 1.2X to 3.6X speed-up

AFS-XT "green" (solver + RC reduction): 2.9x to 11.5x speed-up

There was one outlier, a 56x speed-up on "green" (solver + RC reduction).

The AFS default simulation was running very slow (and so was every other

simulator), so we stopped it early due to time constraints, and then

extrapolated the total runtime based on the time-point reached in the

transient analysis. i.e. 2,446 sec is an estimated old AFS runtime.

This averaged to AFS-XT "green" being 8.2x faster than the old AFS

These benchmarks were for 7nm and 16nm TSMC designs, but we're also

successfully using AFS-XT on 5nm designs.

- [ Anon SPICE User ]

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

HOW MENTOR AFS-XT BENCHMARKS AGAINST CADENCE SPECTRE-X

So my [ Anonymous SPICE User ] didn't have access to CDNS Spectre-X; so he

could only benchmark against the old AFS. But, damn it!, I want to know

how AFS-XT benches vs. Spectre-X!!! gRRR!

Then I remembered a comment from an early 2019 Spectre-X benchmark:

- from two early 2019 Spectre-X user benchmarks

So, doing the simple logical deduction ...

- Spectre-X benches "neck-and-neck" with the old AFS

- the new AFS-XT benches 3x to 11x faster than the old AFS

Therefore if A = B and B = C, then A = C

- i.e. the new AFS-XT benches 3x to 11x faster than Spectre-X

(Sorry, Anirudh. Congrats, Ravi.)

- John Cooley of DeepChip.com

---- ---- ---- ---- ---- ---- ----

Related Articles

Cadence Spectre-X skeptics & early sightings is Best of 2019 #2b

SCOOP -- Anirudh is launching a new Spectre-X SPICE at this DAC'19

Join

Index

Next->Item

|

|